Standard di tensione I/O e il loro ruolo nel garantire che i microcontroller parlino la stessa lingua

Immagina di parlare la tua lingua madre con una persona straniera (Figura 1) e scoprire che non solo non ti capisce, ma che "sì" nella tua lingua significa "no" nella sua. Questo è esattamente ciò che accade quando due circuiti integrati (CI) con standard I/O incompatibili tentano di comunicare. Il risultato è, nel migliore dei casi, confusione e, nel peggiore, danni all'hardware.

Figura 1: Immagine generata dall'IA che simboleggia la confusione derivante dall'utilizzo di diversi standard I/O. (Immagine generata dall'IA)

Figura 1: Immagine generata dall'IA che simboleggia la confusione derivante dall'utilizzo di diversi standard I/O. (Immagine generata dall'IA)

I microcontroller funzionano con la logica binaria basata su 0 e 1. Esistono intervalli di tensione che corrispondono a questi livelli logici. Ad esempio, un microcontroller può leggere uno '0' logico come un valore qualsiasi inferiore a 0,3 V e un '1' come un valore qualsiasi superiore a 2,7 V, fino a 3,3 V. Ma un altro microcontroller legge un '1' come un valore qualsiasi tra 1,2 V e 1,8 V. Se il primo microcontroller invia un segnale da 3,3 V al secondo (Figura 2), potrebbe superare la tolleranza di tensione del dispositivo ricevente, causando potenzialmente danni permanenti.

Figura 2: Rappresentazione di due CI con standard IO incompatibili che comunicano. (Immagine generata dall'IA)

Figura 2: Rappresentazione di due CI con standard IO incompatibili che comunicano. (Immagine generata dall'IA)

Ecco perché comprendere e gestire la compatibilità della tensione I/O è fondamentale nella progettazione di sistemi embedded. Senza una corretta traslazione di livello o di tensione, anche una semplice connessione tra due chip può dare origine a comportamenti imprevedibili o a guasti hardware.

Il ruolo degli standard di tensione I/O

Gli standard di tensione I/O definiscono i livelli di tensione accettabili per i segnali logici digitali, specificando ciò che costituisce un valore logico alto (1) o basso (0). Questi standard garantiscono che i dispositivi possano interpretare correttamente i segnali e rispondere in modo appropriato. In assenza di uno standard concordato su questi livelli, i dispositivi potrebbero interpretare male i segnali o non riuscire a comunicare tra loro.

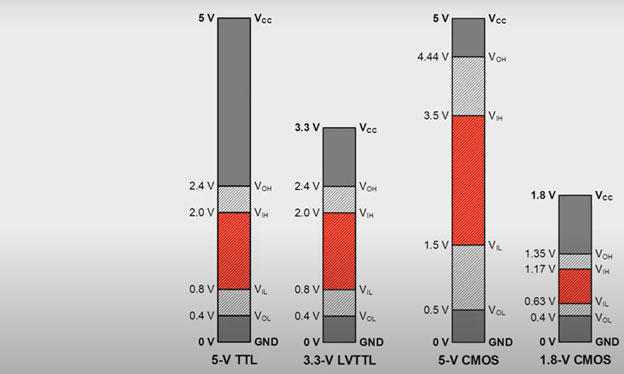

Terminologie definite dagli standard:

- VIH (alta tensione in ingresso): tensione minima riconosciuta come logica alta.

- VIL (bassa tensione in ingresso): tensione massima riconosciuta come logica bassa.

- VOH (alta tensione in uscita): tensione minima in uscita riconosciuta come logica alta.

- VOL (bassa tensione in uscita): tensione massima in uscita riconosciuta come logica bassa.

Per una comunicazione efficace, i livelli di uscita di un dispositivo devono rientrare nell'intervallo di ingresso accettabile del dispositivo ricevente.

Standard I/O sbilanciati

Gli standard di ingresso/uscita (I/O) sbilanciati (SIO) (Figura 3) sono tra quelli più diffusi e utilizzano un singolo filo collegato a una messa a terra comune per il trasferimento del segnale. Quando si tratta di progetti a bassa velocità e bassa complessità, i SIO rappresentano un'alternativa più semplice ed economica rispetto agli standard di segnalazione differenziale, che utilizzano due segnali complementari.

Il metallo-ossido-semiconduttore con accoppiamento complementare a bassa tensione (LVCMOS) è uno standard sbilanciato comune, spesso indicato in alcuni contesti come LVMOS. In genere, LVCMOS funziona a 1,8 V, 2,4 V o 3,3 V e definisce soglie specifiche per valori logici alti e bassi. La semplicità degli standard SIO ha un costo: i SIO come LVCMOS sono sensibili al rumore e al deterioramento del segnale su lunghe distanze o alle alte frequenze. Quando si interfaccia LVCMOS con dispositivi che funzionano in domini di tensione diversi, è fondamentale utilizzare i traslatori di livello per garantire la corretta compatibilità di tensione.

Figura 3: Livelli di tensione di diversi standard I/O. (Immagine per gentile concessione di Texas Instruments)

Figura 3: Livelli di tensione di diversi standard I/O. (Immagine per gentile concessione di Texas Instruments)

Sfide nell'interfacciamento I/O

1. Disadattamento di tensione

Il problema più comune legato all'interfacciamento di dispositivi che funzionano a livelli diversi di tensione è il disadattamento di tensione. Ad esempio, collegare un'uscita da 3,3 V a un ingresso da 1,8 V senza modificare il livello può danneggiare il dispositivo a bassa tensione (Figura 2).

Per attenuare questo problema, è necessario assicurarsi che i livelli di alta tensione in ingresso (VIH) e bassa tensione in ingresso (VIL) di un CI corrispondano a quelli di alta tensione in uscita (VOH) e bassa tensione in uscita (VOL) dell'altro.

2. Integrità del segnale

Alle alte velocità, le riflessioni, la sovraoscillazione e la diafonia possono alterare i segnali. Una corretta terminazione, l'adattamento di impedenza e lo sbroglio delle piste sono essenziali per mantenere pulite le transizioni del segnale.

3. Domini di alimentazione elettrica

Nei sistemi con più linee di tensione, occorre prestare attenzione a isolare o traslare i segnali tra i domini. Le soluzioni più comuni sono i traslatori di livello, i divisori di tensione o le configurazioni a drain aperto con resistori pull-up.

Famiglie logiche avanzate: LVPECL, CML, VML e LVDS

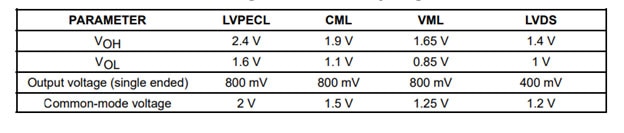

Nei sistemi di comunicazione ad alta velocità sono utilizzate famiglie logiche come LVPECL (logica accoppiamento emettitore positiva bassa tensione), CML (logica della modalità di corrente) e VML (logica della modalità di tensione) (Tabella 1). Queste offrono transizioni più rapide e una migliore immunità al rumore, ma richiedono un'attenta progettazione:

- LVPECL: funziona a circa 3 V, con segnalazione differenziale e prestazioni ad alta velocità

- CML: utilizza sorgenti a corrente costante per una commutazione rapida e un basso jitter

- VML: meno comune, ma offre segnalazione in modalità tensione con oscillazione indipendente dal carico

- LVDS: ampiamente utilizzata per la segnalazione differenziale a bassa potenza e velocità moderata

Tabella 1: Parametri di tensione per livello logico LVPECL, CML, VML e LVDS. (Immagine per gentile concessione di Texas Instruments)

Tabella 1: Parametri di tensione per livello logico LVPECL, CML, VML e LVDS. (Immagine per gentile concessione di Texas Instruments)

Best practice per l'interfacciamento I/O

- Controllare sempre i valori VIH, VIL, VOH e VOL nelle schede tecniche.

- Utilizzare i traslatori di livello quando si interfacciano domini di tensione.

- Eseguire test preliminari e frequenti con oscilloscopi e analizzatori logici.

L'interfacciamento I/O non consiste semplicemente nel collegare i pin, bensì nel garantire che ogni segnale sia interpretato esattamente come previsto. Più i sistemi embedded diventano complessi e operano su più domini di tensione e famiglie logiche, più la buona padronanza della compatibilità I/O diventa importante.

Conoscendo gli standard di tensione, anticipando il disadattamento e applicando le best practice, possiamo progettare sistemi solidi e affidabili che comunicano in modo chiaro e senza errori di traslazione. Tuttavia, se è necessario interfacciare CI con standard I/O diversi, un modo per attenuare il disadattamento nel livello del segnale consiste nell'utilizzare i traslatori di livello.

Traslatore di livello

Un traslatore di livello (LS), noto anche come traslatore di tensione, è un circuito utilizzato nei sistemi integrati per interfacciare in modo sicuro componenti che funzionano a livelli di tensione diversi. Supponiamo che un microcontroller che funziona a 3,3 V debba comunicare con un sensore che funziona con una logica a 1,8 V: il traslatore di livello garantisce che i segnali siano traslati correttamente tra i due, senza alcun rischio di danni o errori logici. A seconda del protocollo utilizzato, i traslatori di livello possono essere unidirezionali o bidirezionali. I LS sono comunemente implementati utilizzando MOSFET, circuiti integrati buffer o chip traslatori dedicati. Svolgono un ruolo fondamentale nel mantenimento dell'integrità del segnale e nella protezione dei componenti in ambienti a tensione mista.

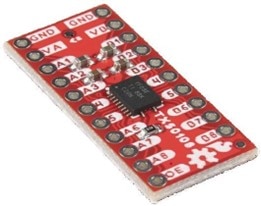

Figura 4: Modulo traslatore di livello a 8 canali. (Immagine per gentile concessione di SparkFun)

Figura 4: Modulo traslatore di livello a 8 canali. (Immagine per gentile concessione di SparkFun)

Altre risorse

Have questions or comments? Continue the conversation on TechForum, DigiKey's online community and technical resource.

Visit TechForum