Come inserire RISC-V nel corso di architettura informatica usando RVfpga.

Cari professori e amici,

la didattica a distanza è comoda e ci ha salvato durante la pandemia, ma le lezioni in presenza sono tutt'altra cosa! Si prova un maggior coinvolgimento con i colleghi che cercano di padroneggiare la stessa materia.

Siamo nel bel mezzo di una serie globale di workshop per "formare gli insegnanti" su come utilizzare RISC-V nei corsi di architettura dei computer e nella progettazione di sistemi su chip (SoC). Abbiamo iniziato l'anno scorso negli Stati Uniti e abbiamo partecipato a diversi eventi in Europa. Di particolare rilievo è il workshop di dicembre nella Silicon Valley a cui hanno partecipato quasi 60 tra insegnanti e formatori!

Ora ci stiamo dirigendo verso est: Israele, Giappone, Taiwan, Corea e Cina.

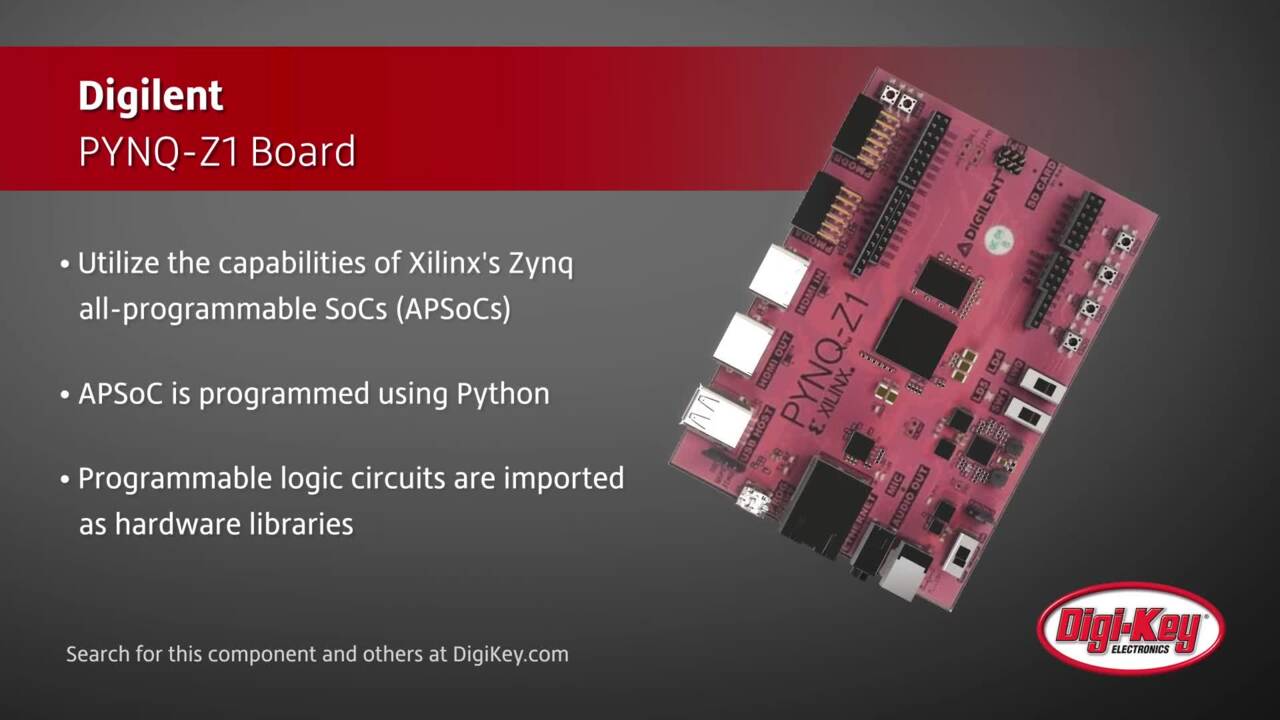

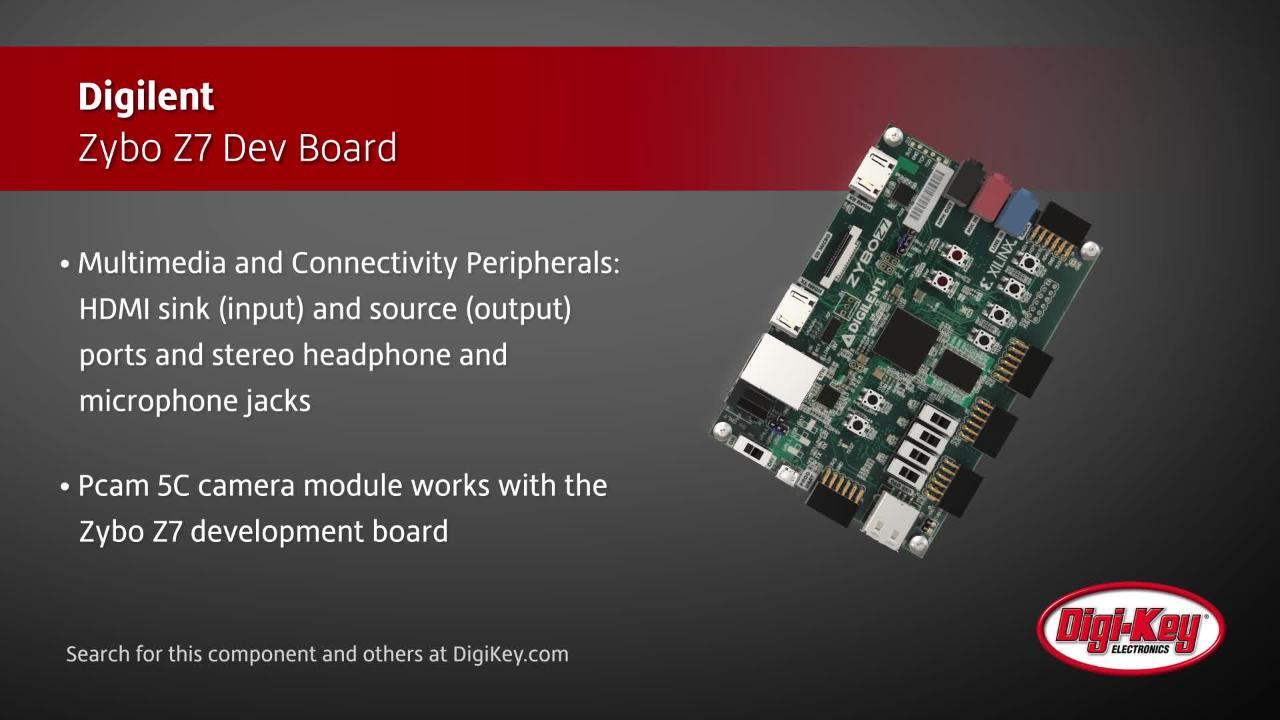

I partner RVfpga, tra cui DigiKey, stanno lavorando con noi per realizzare questa iniziativa.

Per raggiungere questo obiettivo, vi chiediamo un giorno del vostro tempo così da permettere alla nuova generazione di studenti di informatica e di ingegneria di acquisire una reale competenza sull'architettura dei computer e su quella del set di istruzioni RISC-V.

Che cos'è RVfpga?

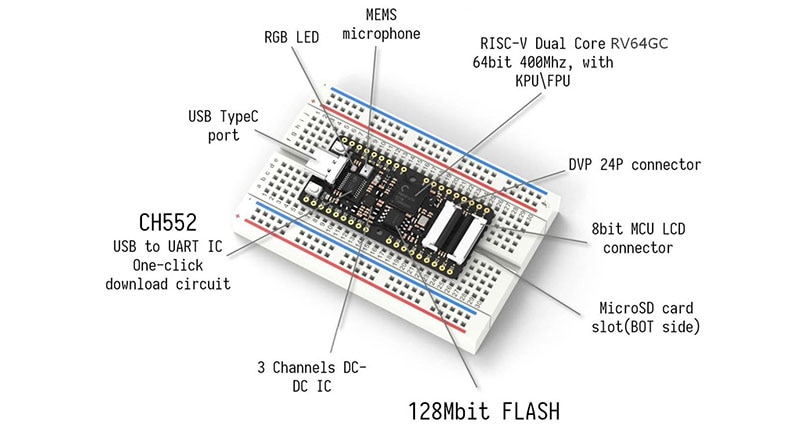

Questo workshop RVfpga in presenza, della durata di un giorno, presenta un sistema commerciale RISC-V mirato a un FPGA, discute la teoria, l'architettura e la struttura del corso e illustra come utilizzare i laboratori pratici come parte del corso RVfpga completo.Il corso esplora i fondamenti dell'architettura dei computer utilizzando il core RISC-V SweRV EH1 di Western Digital, open-source, completamente verificato e già su chip, destinato a un FPGA Artix 7 di Xilinx su scheda di sviluppo Nexys A7 di Digilent. Tutti avranno un'esperienza pratica con la piattaforma FPGA e strumenti software che consentiranno di iniziare rapidamente una volta tornati alla propria università.

SweRV non è una "materia teorica". È una realtà, utilizzata nelle GPU di Imagination e nelle unità a stato solido di Western Digital.

Che cosa apprenderete?

- Il workshop mostra come implementare e mettere in funzione rapidamente il sistema FPGA RISC-V e gli strumenti RISC-V

- Descriviamo ciascuno dei laboratori e lavoriamo su una loro selezione in modo pratico

- Parleremo anche di come integrare RVfpga nel vostro piano di studi

Gli argomenti specifici includono:

- Installare gli strumenti (che incoraggiamo prima del workshop)

- Indirizzare il core SweRV EH1 RISC-V e il SoC verso un FPGA

- Programmare il SoC RISC-V

- Aggiungere più funzionalità al SoC RISC-V

- Analizzare e modificare il core RISC-V e la gerarchia della memoria

Chi dovrebbe partecipare?

- È fondamentalmente un evento "Formare gli insegnanti", di grande valore per gli insegnanti di EE, CS e CE che vogliono insegnare l'architettura dei computer.

- I formatori nelle società commerciali e i neolaureati che pensano a una carriera nell'insegnamento o come progettisti di chip ne trarranno grande beneficio

Connettività di rete

È una grande opportunità per creare nuovi legami e rinfrescare quelli esistenti con i colleghi professori che desiderano mantenere i loro corsi aggiornati. Aiutaci a diffondere la notizia e porta i tuoi colleghi.

Incontrate gli innovatori che stanno valutando RISC-V per progetti start-up e i formatori aziendali che hanno bisogno di materiale eccellente per addestrare i nuovi assunti.

I nostri formatori:

Grazie alla collaborazione con accademici qualificati ed esperti di altre aziende che lavorano su RISC-V, abbiamo a disposizione alcuni degli istruttori più esperti al mondo.

ASEE Baltimore e UCSC Santa Clara

Sarah Harris è professore di ingegneria elettrica e informatica all'Università del Nevada, Las Vegas. Sarah Harris ha conseguito M.S. e Ph.D. presso la Stanford University. È coautrice di tre famosi libri di testo: Digital Design and Computer Architecture, 2a edizione (2007), ARM Edition (2015), e RISC-V Edition (2021). I suoi interessi di ricerca includono l'architettura dei computer e le applicazioni dei sistemi embedded oltre all'apprendimento automatico e all'ingegneria biomedica e alla robotica.

Taiwan

Michio Abe, esperto di architetture di CPU RISC. È direttore vendite e soluzioni presso MIPS LLC in Giappone. La sua carriera è iniziata in NEC nel 1985 e ha partecipato allo sviluppo delle CPU MIPS, comprese quelle originali di NEC nel 1991. A ciò ha fatto seguito lo sviluppo di SoC per veicoli con MIPS e altri core e architetture. Dal 2015 è responsabile di promozione e marketing delle CPU MIPS in Giappone, inizialmente come parte di Imagination Technologies e ora come azienda autonoma.

Il nostro anfitrione locale è il Prof. Brian Lin di NTUST Taipei.

FPL 2023 Göteborg

Daniel A. Chaver Martínez si è laureato in fisica all'Università di Santiago di Compostela (USC) nel 1998 e in ingegneria elettronica all'Università Complutense di Madrid (UCM) nel 2000. Ha sviluppato il suo dottorato dal 2000 al 2006 all'UCM. Fin dagli anni 2000, ha insegnato in molti corsi relativi all'architettura dei computer. I suoi attuali interessi di ricerca includono tecniche architettoniche per la cache e le memorie non volatili e la programmazione del sistema operativo per i multiprocessori asimmetrici. Dal 2015, collabora con Imagination Technologies nello sviluppo di alcuni processori e materiali didattici.

Serie di workshop (data e luogo)

| Data | Sede/evento | Città, Paese | Formato | Registrazione |

|

25 - 28 giugno |

ASEE Conference | Baltimora, Stati Uniti |

Paper: RVfpga: Corso di architettura informatica e MOOC con l'utilizzo di un RISC-V SoC per FPGA e simulazione |

https://nemo.asee.org/public/conferences/327/registration |

| 5 e 6 luglio |

NTUST |

Taipei, Taiwan |

DUE workshop RVfpga di un giorno in presenza, in inglese (con supporto per mandarino e giapponese) |

https://www.eventbrite.co.uk/e/549461984587 [eventbrite.co.uk] https://www.eventbrite.co.uk/e/602617443997 [eventbrite.co.uk] |

| Data di ottobre non fissata | Università di Zhejiang |

Hangzhou, Cina |

Workshop RVfpga di mezza giornata in presenza, in cinese. Trainer: Prof. Liu, Peng e Xi, Yuhao, Zhejiang University, Hangzhou |

Da definire |

| 5 settembre 9.00 - 13.00 |

FPL 2023 |

Chalmers University, Göteborg, Svezia |

Workshop RVfpga di mezza giornata in presenza, in inglese (La registrazione per il solo workshop è di ~USD 120) |

https://2023.fpl.org/attend/registration |

9 novembre |

UCSC - Training Center, Silicon Valley |

Santa Clara, CA - USA |

Workshop RVfpga di un giorno in presenza, in inglese |

https://www.eventbrite.co.uk/e/rvfpga-understanding-computer-architecture-in-person-workshop-nov-9th-tickets-654132025497 |

Ulteriori informazioni

- Informazioni su IUP e RVfpga: https://university.imgtec.com/teaching-download/

- Blog RISC-V: https://blog.imaginationtech.com/how-rvfpga-understanding-computer-architecture-will-give-under-grads-real-world-skills

- Introduzione a RISC-V: https://www.digikey.com/en/resources/risc-v

Ti aspettiamo!

Cordiali saluti,

Robert C.W. Owen

Principal Consultant: Worldwide University Programme

Have questions or comments? Continue the conversation on TechForum, DigiKey's online community and technical resource.

Visit TechForum