Buffer e generatori di clock PCIe®

Con i dispositivi 9DBL0x e 9FGL0x Renesas offre una generazione di clock PCIe Gen1-4 per schede riser, storage, dispositivi di rete, JBOD, comunicazioni e punti di accesso

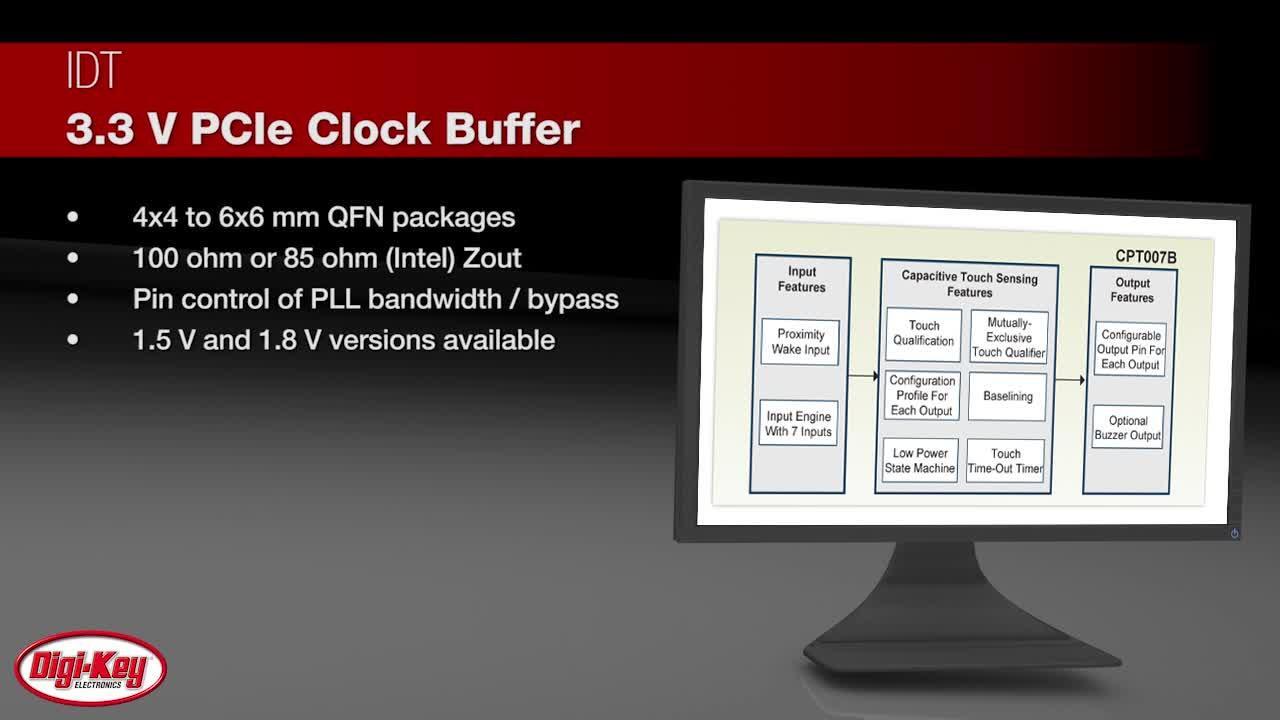

I buffer 9DBL0x PCIe di Renesas sono membri a 3,3 V della famiglia di PCIe a piena funzionalità di Renesas. 9DBL0x supporta sistemi PCIe Gen1-4 (CC) con clock comune (CC) e PCIe con clock di riferimento separato a divisione indipendente (SRIS). Offrono una scelta delle terminazioni di uscita integrate capaci di fornire il collegamento diretto a linee di trasmissione di 85 o 100 Ω.

I buffer 9DBL0x PCIe di Renesas sono membri a 3,3 V della famiglia di PCIe a piena funzionalità di Renesas. 9DBL0x supporta sistemi PCIe Gen1-4 (CC) con clock comune (CC) e PCIe con clock di riferimento separato a divisione indipendente (SRIS). Offrono una scelta delle terminazioni di uscita integrate capaci di fornire il collegamento diretto a linee di trasmissione di 85 o 100 Ω.

I generatori di clock dispositivi PCIe 9FGL0x di Renesas appartengono anche alla famiglia di PCIe a piena funzionalità di Renesas a 3,3 V. Questi dispositivi hanno 2, 4, 6 e 8 abilitazioni uscita per la gestione del clock e supportano due livelli di divisione di spettro diverse in aggiunta a Off divisione. 9FGL0x supporta architetture di clock PCIe Gen1-4 a clock comune (CC) e PCIe con architetture clock di riferimento separato senza divisione (SRnS) e clock di riferimento separato a divisione indipendente (SRIS).

I dispositivi 9DBL0xP1 e 9FGL0xP1 possono essere programmati in fabbrica per la configurazione SMBus predefinita dell'accensione definita dall'utente.

- Conforme a PCIe Gen1-2-3-4 CC in modo ZDB

- Conforme a PCIe Gen2 SRIS in modo ZDB

- Supporta PCIe Gen2-3 SRIS in modo fanout

- Supporta clock SRnS PCIe

- Collegamento diretto a linee di trasmissione a 100 Ω (xx42) o 85 Ω (xx52)

- Consente di risparmiare 8, 16, 24 o 32 resistori rispetto ai dispositivi PCIe standard

- Tollera la divisione di spettro; consente di ridurre le EMI

- Larghezza di banda PLL selezionabile da pin/SMBus e bypass PLL

- Riduce al minimo il jitter di fase per ogni applicazione

- Il dispositivo contiene la configurazione predefinita

- Interfaccia di SMBus non richiesta per il funzionamento del dispositivo.

- Facile accoppiamento in c.a. ad altre famiglie di logica

- Vedere la nota applicativa AN-891 di Renesas

- Salvaspazio, 24 pin 4 x 4 mm (9DBL02), 32 pin 5 x 5 mm (9DBL04), 32 pin 5 x 5 mm (9DBL06) o VFQFPN 48 pin 6 x 6 mm (9DBL08); occupa spazio minimo su scheda

-

li>Conforme a PCIe Gen1-2-3-4 CC

- Conforme a PCIe Gen2-3 SRIS

- Collegamento diretto a linee di trasmissione a 100 Ω (xx41) o 85 Ω (xx51)

- Consente di risparmiare 8, 16, 24 o 32 resistori rispetto ai dispositivi PCIe standard

- Divisione 0%, -0,25% o -0,5% selezionabile tramite pin/SMBus su uscite DIF

- Riduce al minimo le EMI e il jitter di fase per ogni applicazione

- Supporta clock SRnS PCIe

- Una uscita REF LVCMOS a 3,3 V con supporto di riattivazione LAN (WoL)

- Facile accoppiamento in c.a. ad altre famiglie di logica

- Vedere la nota applicativa AN-891 di Renesas

- Salvaspazio, 24 pin 4 x 4 mm (9FGL02), 32 pin 5 x 5 mm (9FGL04), 40 pin 5 x 5 mm (9FGL06) o VFQFPN 48 pin 6 x 6 mm (9FGL08); occupa spazio minimo su scheda

9DBL0x PCIe Zero-Delay Buffers

| Immagine | Codice produttore | Descrizione | Quantità disponibile | Prezzo | Vedi i dettagli | |

|---|---|---|---|---|---|---|

|  | 9DBL0242BKILF | IC CLK FANOUT/BUFF ZD 24VFQFPN | 364 - Immediatamente | $2.36 | Vedi i dettagli |

|  | 9DBL0442BKILF | IC CLK FANOUT/BUFF ZD 32VFQFPN | 0 - Immediatamente | See Page for Pricing | Vedi i dettagli |

|  | 9DBL0641BKILF | IC CLK FANOUT/BUFF ZD 40VFQFPN | 0 - Immediatamente | See Page for Pricing | Vedi i dettagli |

|  | 9DBL0841BKILF | IC CLK FANOUT/BUFF ZD 48VFQFPN | 0 - Immediatamente | See Page for Pricing | Vedi i dettagli |