Un ADC può essere solo un generatore di numeri casuali?

2025-10-22

Quanto è valido un ADC? La domanda non riguarda il numero di bit di risoluzione che offre; potrebbe infatti sorprendere sapere che un ADC a 16 bit non sempre fornisce 16 bit di informazioni utili! "Molti ADC a 16 bit funzionano in realtà come ADC a 7 bit e generatori di numeri casuali a 9 bit", spiega Mike Stone in "Choosing an ADC". Questo articolo mostra come stabilire se un ADC generi numeri più casuali che utili, insieme ad alcuni semplici modi per ridurre la casualità.

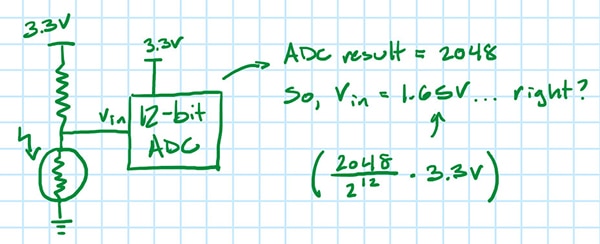

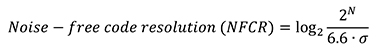

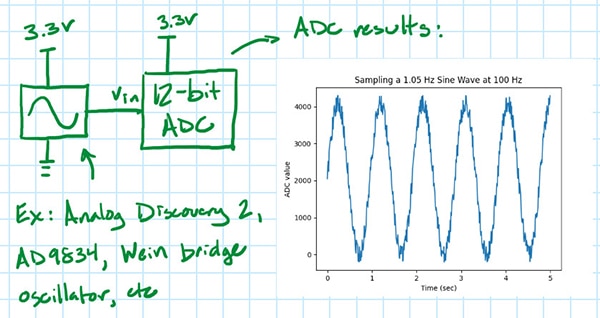

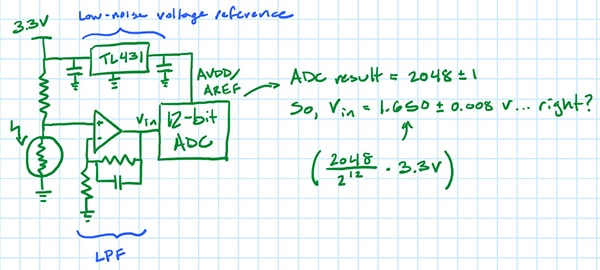

Prendiamo in esame una configurazione semplificata: un ADC che misura la tensione di un fotoresistore. Se l'ADC a 12 bit della Figura 1 (con VFS = 3,3 V) indica un valore di 2048, questo significa che la tensione del fotoresistore è di 1,65 V?

Figura 1: Configurazione semplificata di un ADC per la misurazione della tensione di un fotoresistore. (Immagine per gentile concessione di Nathan Jones)

Figura 1: Configurazione semplificata di un ADC per la misurazione della tensione di un fotoresistore. (Immagine per gentile concessione di Nathan Jones)

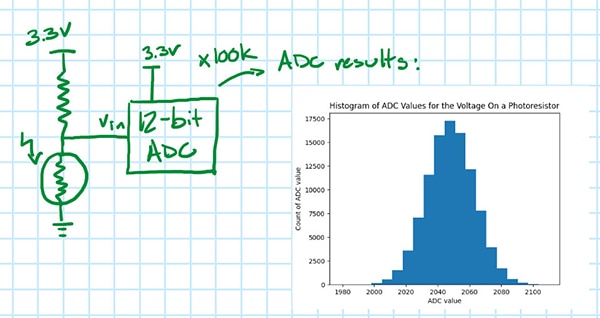

No, non proprio! Per dimostrarlo, prendiamo un secondo campione, poi un terzo e, anzi, prendiamo 100.000 campioni e tracciamone i risultati. Si vedrà una distribuzione di valori ADC (Figura 2); se non è cambiato nulla nell'impostazione, uno qualsiasi di questi potrebbe essere la vera tensione del fotoresistore, e il candidato più probabile è il valore medio di tutti i campioni.

Figura 2: L'inserto mostra l'istogramma dei valori ADC di 100.000 campioni della tensione del fotoresistore. (Immagine per gentile concessione di Nathan Jones)

Figura 2: L'inserto mostra l'istogramma dei valori ADC di 100.000 campioni della tensione del fotoresistore. (Immagine per gentile concessione di Nathan Jones)

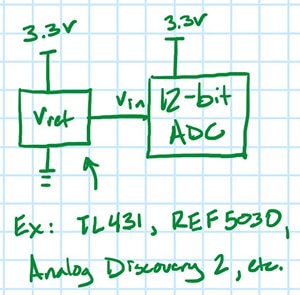

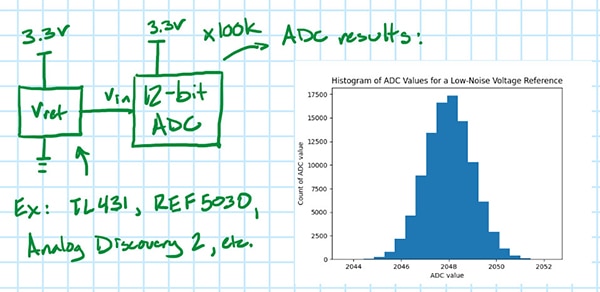

Questo porta a un'altra domanda. In parte, questa variazione potrebbe essere dovuta a variazioni effettive del segnale di ingresso? Sì, è plausibile. Per verificarlo, sostituiamo il divisore resistivo con un riferimento di tensione (Figura 3) avente un livello di rumore noto e ripetiamo l'esperimento.

Figura 3: Nuova configurazione di prova con un riferimento di tensione al posto del divisore resistivo. (Immagine per gentile concessione di Nathan Jones)

Figura 3: Nuova configurazione di prova con un riferimento di tensione al posto del divisore resistivo. (Immagine per gentile concessione di Nathan Jones)

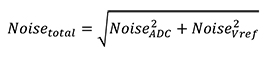

In linea di principio, il riferimento di tensione utilizzato dovrebbe avere un livello di rumore inferiore a 1/3 del livello di rumore previsto nell'ADC (es., se si prevede che l'ADC abbia un rumore di ±1 LSB [che sarebbe ±0,8 mV utilizzando l'ADC dell'esempio precedente], allora in teoria il riferimento di tensione dovrebbe avere un livello di rumore inferiore a 0,27 mVpp); in caso contrario, si prevede che tutto il rumore misurato provenga dall'ADC, in base al fatto che il rumore non correlato si somma in quadratura (equazione 1).

[1]

[1]

Se NoiseVref=NoiseADC/3 allora Noisetotal=1,054 × NoiseADC. Ciò significa che il riferimento di tensione contribuisce solo al 5,4% del rumore totale, una quantità trascurabile. Se si scopre che il riferimento di tensione è più rumoroso di 1/3 del rumore dell'ADC, basta ricordarsi di sottrarre il suo contributo dalla deviazione standard misurata (vedere l'equazione 2).

[2]

[2]

Come conoscere il livello di rumore di una sorgente di tensione

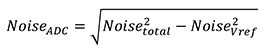

Il modo più semplice è trovarlo nella scheda tecnica. Ecco un esempio tratto dalla scheda tecnica di REF5030 di Texas Instruments, che mostra un livello di rumore di 9 μVpp.

Figura 4: Estratto dalla scheda tecnica di REF5030 che mostra le specifiche del rumore della tensione di uscita. (Immagine per gentile concessione di Texas Instruments)

Figura 4: Estratto dalla scheda tecnica di REF5030 che mostra le specifiche del rumore della tensione di uscita. (Immagine per gentile concessione di Texas Instruments)

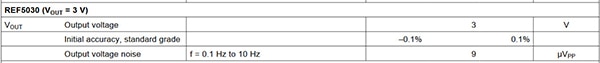

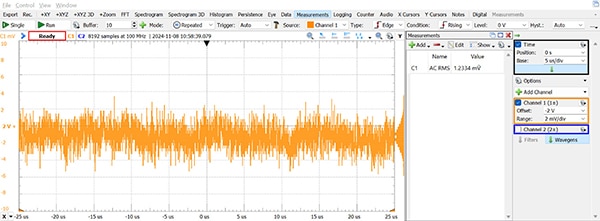

Se la scheda tecnica non riporta un livello di rumore (o se si vuole solo verificarne il valore), è sufficiente misurarlo con un oscilloscopio, anche se prima è necessario conoscere il rumore di fondo dell'oscilloscopio. A tal fine, è possibile collegare a massa uno degli ingressi dell'oscilloscopio e misurare il valore efficace delle variazioni del segnale osservato. La Figura 5 mostra il risultato di questa operazione con uno strumento Analog Discovery 2 (AD2), che dimostra che il rumore efficace è di circa 0,9 mV. È interessante notare che questo valore diminuisce (fino all'intervallo dei µV) se si aumenta la base temporale oltre 8 µs/div, presumibilmente perché AD2 utilizza il sovracampionamento e la decimazione per aumentare la risoluzione efficace.

Figura 5: Grafico del livello di rumore di fondo dell'oscilloscopio Analog Discovery 2. (Immagine per gentile concessione di Nathan Jones)

Figura 5: Grafico del livello di rumore di fondo dell'oscilloscopio Analog Discovery 2. (Immagine per gentile concessione di Nathan Jones)

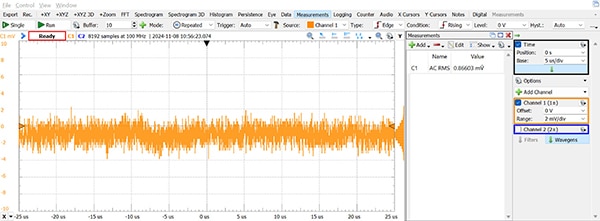

Quando si misura la sorgente di tensione, le variazioni del segnale dell'oscilloscopio sono il risultato del rumore combinato della sorgente di tensione e dell'oscilloscopio. A patto che queste sorgenti di rumore non siano correlate (lo sono), Noisemeasured=√(Noise²Scope+Noise²Vref) e NoiseVref=√(Noise²measured-Noise²Scope), come sopra. Misurando un segnale di 2 Vc.c. generato da AD2, il rumore è risultato pari a 1,2 mV (Figura 6).

Figura 6: Questo grafico di un segnale di 2 V c.c. indica che il rumore dell'oscilloscopio era di 1,2 mV. (Immagine per gentile concessione di Nathan Jones)

Figura 6: Questo grafico di un segnale di 2 V c.c. indica che il rumore dell'oscilloscopio era di 1,2 mV. (Immagine per gentile concessione di Nathan Jones)

Ciò indica che anche il generatore di segnale di AD2 ha un livello di rumore di circa 0,9 mV. Questo valore è sufficientemente basso per testare un ADC a 10 bit (0,9 mV è appena meno di 1/3 di un LSB per un ADC a 10 bit con lettura a fondo scala di 3,3 V); per qualsiasi ADC a risoluzione superiore, questo rumore dovrebbe essere tenuto a mente nelle misurazioni.

Figura 7: L'inserto mostra il nuovo istogramma dei valori ADC di 100.000 campioni della tensione del fotoresistore con il riferimento di tensione. (Immagine per gentile concessione di Nathan Jones)

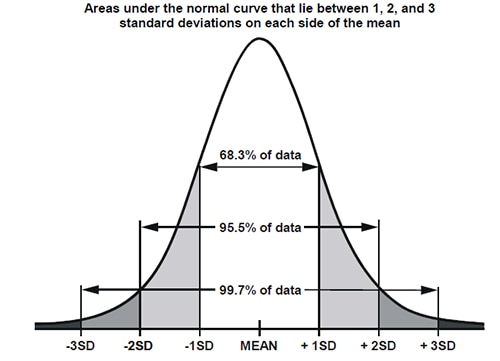

Molto meglio! Si noti ora come il secondo istogramma (Figura 7) si estende solo fino a 2052 sull'asse delle ascisse (la distribuzione su tale grafico [Figura 8] ha una deviazione standard di 1 LSB), mentre il primo grafico si estendeva fino a 2100 (aveva una deviazione standard di 15 LSB). Questo si chiama test dell'istogramma c.c. per un ADC e la deviazione standard indica efficacemente il rumore dell'ADC: ogni volta che si misura un valore con l'ADC, vi è una probabilità solo del 68% che il valore reale sul pin analogico sia effettivamente entro ±1 DS di tale valore, ma esiste una probabilità del 99,7% che il valore reale rientri in ±3 DS di tale valore.

Figura 8: Curva della distribuzione con deviazioni standard. (Immagine per gentile concessione di https://i.sstatic.net/jkMDV.png)

Figura 8: Curva della distribuzione con deviazioni standard. (Immagine per gentile concessione di https://i.sstatic.net/jkMDV.png)

Convertendo questa deviazione standard da LSB a volt si ottiene il rumore riferito all'ingresso dell'ADC (Equazione 3).

![Input - referred noise [V_RMS ]=(σ∙V_FS)/2^N Equazione 3](http://sc-c.digikeyassets.com/-/media/Images/Article%20Library/TechZone%20Articles/2025/October/Can%20an%20ADC%20Be%20Just%20a%20Random%20Number%20Generator/article-2025october-can-an-adc-be-just-equation3.jpg?la=en&ts=6126a5a1-ecae-4e79-bfb0-97e98cce83fa) [3]

[3]

Se l'ADC ha un rumore così ridotto che tutti i codici ADC rientrano una singola classe, provare a ridurre la tensione di riferimento dell'ADC. Il livello di rumore rimarrà invariato, ma occuperà più codici ADC di prima, e ciò consentirà di trovare un valore adeguato per il rumore riferito all'ingresso.

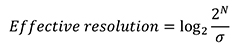

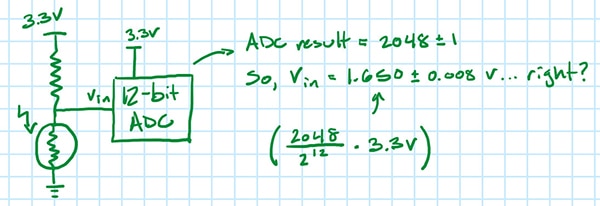

La risoluzione efficace e la risoluzione dei codici privi di rumore (NFCR) di un ADC rappresentano la misura in cui questo rumore limita la risoluzione dell'ADC e sono calcolate dividendo l'intero intervallo di codici ADC in classi ampie solo quanto una (Equazione 4) o 6,6 deviazioni standard (Equazione 5).

[4]

[4]

[5]

[5]

In sostanza, il minor numero di bit effettivi nel risultato è dovuto al fatto che aumenta la possibilità che gli ultimi bit nel risultato dell'ADC siano sbagliati o rumorosi.

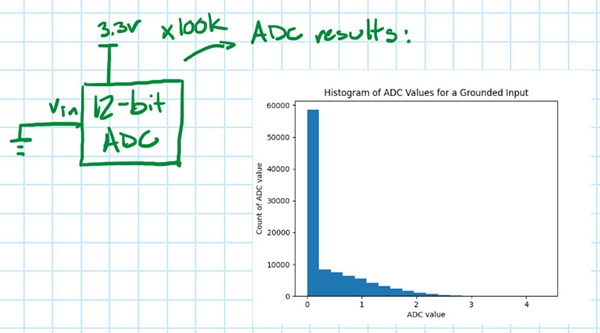

Una versione un po' più semplice del test dell'istogramma c.c. prevede la semplice messa a terra dell'ingresso dell'ADC e la creazione di un istogramma (Figura 9) dei risultati dell'ADC, come è stato fatto per l'oscilloscopio.

Figura 9: L'inserto mostra l'istogramma dei campioni della tensione di uscita dell'ADC con l'ingresso a massa. (Immagine per gentile concessione di Nathan Jones)

Figura 9: L'inserto mostra l'istogramma dei campioni della tensione di uscita dell'ADC con l'ingresso a massa. (Immagine per gentile concessione di Nathan Jones)

La deviazione standard di questo istogramma è anche una misura del rumore dell'ADC (meno i contributi del rumore nella tensione di riferimento dell'ADC, che non influisce sulle letture di 0 V), ma è ottimisticamente bassa. L'ADC probabilmente riporta i valori inferiori a 0 V come se fossero solo 0, quindi nota solo la metà della reale distribuzione del rumore. In questo caso, il rumore dell'ADC può essere approssimato se si presuppone che la distribuzione sia simmetrica rispetto al suo valore medio, cambiando un numero sufficiente di valori mediani in numeri negativi in modo che la distribuzione diventi simmetrica e quindi calcolando la deviazione standard di questo valore (Figura 10).

Figura 10: Specularità dell'istogramma della Figura 9 per approssimare il rumore dell'ADC. (Immagine per gentile concessione di Nathan Jones)

Figura 10: Specularità dell'istogramma della Figura 9 per approssimare il rumore dell'ADC. (Immagine per gentile concessione di Nathan Jones)

D'accordo. Quindi, che cosa possiamo fare con tutto questo rumore? Se la risoluzione dell'ADC rientra comunque nei requisiti del progetto (che fortuna!), tenete presente che ogni misurazione dell'ADC porta con sé un certo grado di incertezza:

- Quando si confrontano due valori ADC, considerateli equivalenti solo se si trovano entro 6,6 σ l'uno dall'altro (per essere sicuri al 99,7% nel confronto) o se si trovano entro σ l'uno dall'altro (per essere sicuri solo al 68%).

- Quando si confronta un valore ADC con una soglia, aggiungete una certa isteresi al confronto della soglia (come fa un termostato) per evitare che il sistema embedded si riattivi al di sopra e al di sotto della soglia solo sulla base del rumore.

Se scoprite che l'ADC non soddisfa più i requisiti del progetto, alcune semplici procedure possono migliorarne le prestazioni. Per quanto riguarda l'hardware, queste includono:

- Utilizzare un riferimento a basso rumore (come REF5030 di Texas Instruments o TL431 di EVVO) per AVCC e AREF

- Garantire una diafonia minima tra i segnali analogici e digitali sulla PCB

- Spegnere la CPU durante le conversioni ADC (se l'MCU supporta l'operazione), per ridurre il rumore digitale

Per quanto riguarda il software, il segnale di ingresso può essere sovracampionato (prendendo la media di N campioni) per ridurre il rumore, anche se ciò ridurrà chiaramente la frequenza di campionamento massima. (In realtà, si potrebbe utilizzare una tecnica chiamata "sovracampionamento e decimazione" per aumentare la risoluzione dell'ADC di una quantità correlata al numero di volte in cui l'ingresso viene sovracampionato.)

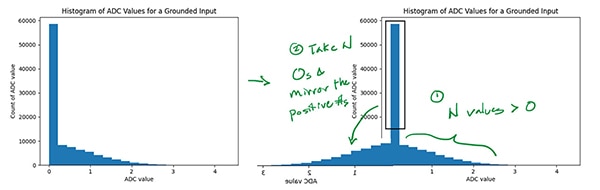

Si supponga che la deviazione standard di un test dell'istogramma c.c. per la configurazione iniziale sia di 1 LSB. Se l'ADC legge 2048, significa ora (con una probabilità del 68%) che il valore reale sia 1,650±0,008 V (Figura 11)?

Figura 11: Supponendo che la deviazione standard della configurazione di Figura 1 sia di 1 LSB e che l'uscita dell'ADC sia 2048, la vera tensione di ingresso è 1,650±0,008 V? (Immagine per gentile concessione di Nathan Jones)

Figura 11: Supponendo che la deviazione standard della configurazione di Figura 1 sia di 1 LSB e che l'uscita dell'ADC sia 2048, la vera tensione di ingresso è 1,650±0,008 V? (Immagine per gentile concessione di Nathan Jones)

Ci siamo quasi, ma non del tutto! Questo perché tutti gli ADC hanno difficoltà a misurare un segnale di ingresso che cambia rapidamente a una certa frequenza, con conseguente imprecisione delle misurazioni (cioè rumore). Sorprendentemente, la frequenza alla quale ciò si verifica può essere ben al di sotto della massima frequenza di campionamento dell'ADC! Ciò significa che un ADC a 12 bit con una frequenza di campionamento di 1 Msps potrebbe non avere una risoluzione di 12 bit per segnali di ingresso vicini a 500 kHz; la risoluzione di quell'ADC potrebbe scendere a 6 bit o anche meno quando la frequenza del segnale di ingresso è così alta. Se si tentasse di misurare un segnale sul fotoresistore superiore a 10 Hz, l'ADC potrebbe non avere una risoluzione di 12 bit.

Per stabilire la capacità di risoluzione dell'ADC con frequenze di ingresso più elevate, inviare un segnale di buona qualità noto (questa volta un'onda sinusoidale) e misurare la corrispondenza dei valori dell'ADC al segnale noto (Figura 12). (L'onda sinusoidale è "abbastanza buona"? Ne riparleremo dopo vi avrò svelato la procedura di esecuzione del test; in questo modo avrà più senso.)

Figura 12: Configurazione del test con un ingresso a onda sinusoidale di buona qualità noto. (Immagine per gentile concessione di Nathan Jones)

Figura 12: Configurazione del test con un ingresso a onda sinusoidale di buona qualità noto. (Immagine per gentile concessione di Nathan Jones)

Per l'onda sinusoidale si può utilizzare un generatore di funzioni (come quelli presenti in molti oscilloscopi USB), un chip DDS (come AD9834 di Analog Devices), oppure si può assemblare un generatore di onde sinusoidali personalizzato (basato su un oscillatore a ponte di Wien o utilizzando un dispositivo MAX7400 di Analog Devices per filtrare in modo passa-basso un'onda quadra, ad esempio). È importante notare che per questo test si devono usare solo frequenze di ingresso che non siano sottomultipli interi della frequenza di campionamento (es., non usare una frequenza di ingresso di 1 kHz se la frequenza di campionamento è di 100 kHz). Questo per evitare di campionare erroneamente l'onda sinusoidale negli stessi punti di ogni ciclo. Inoltre, per sollecitare al massimo l'ADC, impostare l'ampiezza dell'onda sinusoidale di ingresso sul valore massimo che non "taglia" l'uscita (es., qualcosa di leggermente inferiore a 1,65 V per l'ADC negli esempi precedenti).

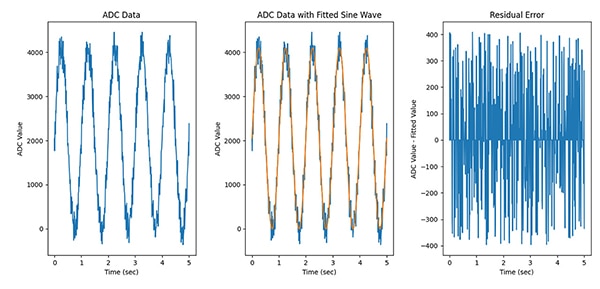

Dopo aver raccolto i risultati dell'ADC, i dati vengono adattati a un'onda sinusoidale per calcolare l'errore residuo. L'adattamento dell'onda sinusoidale può essere eseguito con quasi tutti i dati, ma per ottenere i migliori risultati è necessario che vi siano almeno cinque periodi completi dell'onda sinusoidale in ingresso. È probabile che l'algoritmo di adattamento sinusoidale debba essere inizializzato fornendo le ipotesi iniziali per l'ampiezza, la frequenza, lo spostamento di fase e l'offset (Figura 13).

Figura 13: Utilizzando un algoritmo di adattamento dell'onda sinusoidale, è possibile determinare l'errore residuo. (Immagine per gentile concessione di Nathan Jones)

Figura 13: Utilizzando un algoritmo di adattamento dell'onda sinusoidale, è possibile determinare l'errore residuo. (Immagine per gentile concessione di Nathan Jones)

Questo test è chiamato test dell'adattamento dell'onda sinusoidale per un ADC e il valore efficace dell'errore residuo è una misura della rumorosità dell'ADC a quella specifica frequenza di ingresso. Alle frequenze più basse, il rumore efficace dovrebbe corrispondere al rumore riferito all'ingresso dal test dell'istogramma c.c., ma alle frequenze più alte quasi certamente si deteriorerà a causa delle sorgenti di rumore dipendenti dalla frequenza summenzionate.

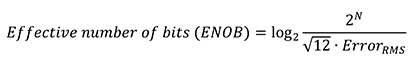

Il valore del rumore efficace ottenuto dal test di adattamento dell'onda sinusoidale può essere utilizzato per calcolare il numero di bit effettivi (ENOB) dell'ADC (Equazione 6), che è il numero di bit di un ADC ideale la cui unica fonte di rumore, il rumore di quantizzazione, ha lo stesso valore efficace del rumore dell'ADC.

[6]

[6]

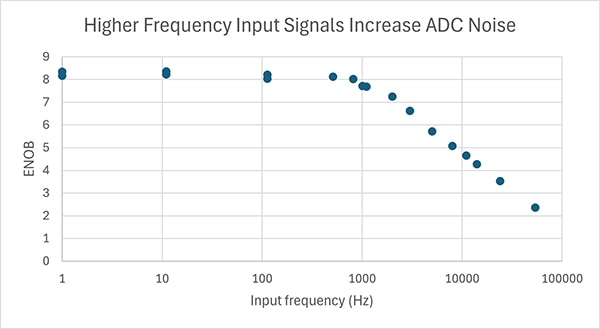

Questo valore è specifico per la frequenza del segnale di ingresso utilizzato. Per avere un quadro più completo dell'ADC, questo test dovrebbe essere ripetuto a frequenze fino al segnale di ingresso di interesse più alto o fino alla metà della frequenza di campionamento massima. Si potrebbe scoprire che il rumore aumenta notevolmente (e l'ENOB diminuisce!) a frequenze ben inferiori alla metà della frequenza di campionamento massima! Ad esempio, abbiamo eseguita questa esatta serie di test sull'ADC di un microcontroller STM32F042K6 di STMicroelectronics e abbiamo tracciato i risultati (Figura 14).

Figura 14: Test del rumore di frequenza per un ADC in un microcontroller STM32F042K6. (Immagine per gentile concessione di Nathan Jones)

Figura 14: Test del rumore di frequenza per un ADC in un microcontroller STM32F042K6. (Immagine per gentile concessione di Nathan Jones)

Anche se l'ADC del microcontroller STM32F042K6 è in grado di campionare a 1 MHz, la risoluzione crolla al di sopra di 1 kHz; se l'intento fosse quello di misurare un segnale a 10 kHz con questo ADC, a quel punto si avrebbero solo circa 5 bit di risoluzione! (Si noti anche che l'ENOB massimo è di circa 8,3; ciò è dovuto a ~10 LSB di rumore anche in corrente continua, che riducono la risoluzione effettiva dell'ADC da 12 bit a circa 8,7 bit. Questi test sono stati condotti su una scheda di sviluppo Nucleo-F042 non modificata di STMicroelectronics; i risultati sarebbero molto migliori utilizzando una qualsiasi delle tecniche summenzionate [D'accordo. Quindi, che cosa possiamo fare con tutto questo rumore?].)

Come conoscere il livello di rumore di un'onda sinusoidale

Come per il riferimento di tensione, se il livello di rumore dell'onda sinusoidale è a priori (cioè, se non è disponibile su una scheda tecnica), è necessario misurarlo con un oscilloscopio. L'uso della tecnica di adattamento dell'onda sinusoidale discussa in precedenza può caratterizzare il rumore del generatore di onda sinusoidale.

- Anzitutto, stabilire il rumore di fondo dell'oscilloscopio collegando l'ingresso a terra e calcolando il valore efficace dell'uscita (come descritto in precedenza nella sezione "Come conoscere il livello di rumore di una sorgente di tensione").

- Quindi, misurare l'uscita del generatore di onda sinusoidale, adattare i risultati a un'onda sinusoidale perfetta e calcolare il valore efficace dei residui. Utilizzare quindi l'equazione 2 per stabilire il rumore del generatore di onda sinusoidale (utilizzando il rumore di fondo dell'oscilloscopio come approssimazione del suo rumore in c.a.).

- Assicurarsi che l'impedenza di uscita del dispositivo collegato al pin analogico sia molto bassa, eventualmente inserendo un amplificatore operazionale per il buffering

- Regolare il clock dell'ADC o il suo tempo di campionamento/mantenimento in modo che sia il più veloce possibile, pur dando al condensatore interno il tempo necessario per caricarsi

- Utilizzare una sorgente di clock ADC a basso jitter e configurare il sistema in modo da prelevare i campioni ADC a intervalli regolari

- Characterizing the Raspberry Pi Pico ADC

- Understanding Data Converters (Texas Instruments)

- Understand SINAD, ENOB, SNR, THD, THD + N, and SFDR so You Don't Get Lost in the Noise Floor (Analog Devices)

- The Good, the Bad, and the Ugly Aspects of ADC Input Noise--Is No Noise Good Noise? (Analog Devices)

- Getting the most out of the SAM D21's ADC (Thea Codes)

- "Analog-to-Digital Converter Testing" (Kent Lundberg)

- Dynamic Tests For A/D Converter Performance (Texas Instruments)

- How to optimize the ADC accuracy in the STM32 MCUs (STM)

- Enhancing ADC resolution by oversampling (Atmel)

- Fundamentals of Precision ADC Noise Analysis (Texas Instruments)

- ADC Gain and Offset Error Calibration on ARM® Cortex®-M0+ Based MCUs (Microchip)

- Sine wave generation via low-pass filtering a square wave

- Understanding the impact of digitizer noise on oscilloscope measurements (EE Times)

- Understanding Effective Number of Bits (Robust Circuit Design)

Nel caso ideale, il livello di rumore dell'onda sinusoidale è inferiore a 1/3 del livello di rumore previsto dall'ADC (cioè, l'onda sinusoidale è "spettralmente pura"), il che renderebbe trascurabile il suo contributo al rumore misurato. Se il livello di rumore dell'onda sinusoidale è superiore a questo, ricordarsi di sottrarlo dal rumore misurato ottenuto dal calcolo dei valori efficaci dell'errore residuo.

Questo test deve essere ripetuto per ogni frequenza di ingresso che si intende utilizzare per testare l'ADC (anche il generatore di onda sinusoidale può avere sorgenti di rumore dipendenti dalla frequenza!)

Che cosa possiamo fare con tutto questo rumore? In primo luogo, si raccomanda di interporre un filtro passa-basso (LPF) tra la sorgente del segnale e l'ADC, con una frequenza di taglio appena superiore al segnale di interesse più alto, per aiutare a limitare il rumore ad alta frequenza (questa è una buona prassi, in generale, per qualsiasi sistema di acquisizione dati). Se tale segnale di interesse a frequenza più alta si trova al di sotto del "ginocchio" nel grafico ENOB rispetto alla frequenza di ingresso, non vi è alcuna perdita di risoluzione. Quando si tenta di misurare i segnali al di sopra del "ginocchio", alcuni accorgimenti possono migliorare la risoluzione alle frequenze più alte. Questi comprendono:

A meno che l'obiettivo non sia un segnale in una banda di frequenze molto ristretta, la cosa più semplice da fare è presupporre che i segnali di ingresso effettivi abbiano lo stesso contenuto di frequenza dalla corrente continua fino alla frequenza di taglio del filtro passa-basso, quindi che il rumore efficace in ogni misurazione ADC sia il rumore efficace medio misurato usando il test di adattamento dell'onda sinusoidale da c.c. fino alla frequenza di taglio. Se si desidera misurare i segnali a banda larga fino a 10 kHz utilizzando il dispositivo STM32F042K6 discusso in precedenza, sarebbe meglio procedere come se l'ADC avesse solo un ENOB di circa 6 bit per ogni misurazione. Questo valore può tranquillamente essere inferiore a quello stabilito con il test dell'istogramma c.c., e ciò indicherebbe una minore certezza in ciascuna delle misurazioni ADC se vi è la possibilità che abbiano un contenuto di frequenza più elevato.

L'ipotesi successiva da considerare è l'aggiunta di un LPF tra il sensore e l'ADC, in modo che il rumore efficace da c.c. fino alla frequenza di taglio sia solo di ±1 LSB. Se l'ADC legge 2048, significa ora (con una probabilità del 68%) che il valore reale sia 1,650±0,008 V (Figura 15)?

Figura 15: L'aggiunta di un filtro passa-basso nel circuito produce un valore reale di 1,650±0,008 V? (Immagine per gentile concessione di Nathan Jones)

Figura 15: L'aggiunta di un filtro passa-basso nel circuito produce un valore reale di 1,650±0,008 V? (Immagine per gentile concessione di Nathan Jones)

Per quanto possa sembrare assurdo, non ancora! Sebbene questo articolo abbia caratterizzato efficacemente il rumore dell'ADC, non ha ancora caratterizzato il suo errore. Al termine dei test qui descritti, l'unica certezza è che due valori ADC sono uguali o diversi. Tuttavia, non è dato sapere se un codice ADC di 2048 corrisponda esattamente a 1,65 V o a un altro risultato. Errori di guadagno, offset e non linearità differenziale (ma non solo) possono significare che la conversione da un codice ADC a una tensione effettiva è più complicata dell'utilizzo di Vin=risultato ADC × VFS/2N. Ma questo è un argomento per un altro articolo!

Riferimenti

Esonero della responsabilità: le opinioni, le convinzioni e i punti di vista espressi dai vari autori e/o dai partecipanti al forum su questo sito Web non riflettono necessariamente le opinioni, le convinzioni e i punti di vista di DigiKey o le sue politiche.