I principi base dei sintetizzatori digitali diretti (DDS), come sceglierli e usarli.

Contributo di Editori nordamericani di DigiKey

2019-03-20

Con il proliferare dei dispositivi wireless, i progettisti devono utilizzare forme d'onda sempre più complesse e variabili per soddisfare i requisiti applicativi in termini di velocità dati, riduzione delle interferenze, costi, ingombri e basso consumo energetico. Queste forme d'onda richiedono sorgenti RF stabili, sintonizzabili su richiesta e agili sia in frequenza che in fase. Allo stesso tempo, devono anche fornire un alto livello di purezza del segnale. La soluzione a questo intreccio di requisiti risiede nei sintetizzatori digitali diretti (DDS).

Il DDS genera forme d'onda analogiche utilizzando metodi digitali, il che permette di sfruttare la programmabilità del digitale, livelli più elevati di integrazione e costi inferiori. Inoltre, il DDS consente un cambiamento quasi istantaneo della frequenza o della fase, rendendolo una fonte primaria per tecniche avanzate di modulazione come la modulazione digitale di frequenza (FSK) e la divisione di spettro, così come l'uso di tecniche di attenuazione delle interferenze come il salto di frequenza. Come risultato, i circuiti integrati DDS stanno rapidamente sostituendo o affiancando i tradizionali circuiti ad aggancio di fase (PLL) e altre sorgenti RF analogiche, offrendo comunque elevata stabilità e purezza del segnale.

Questo articolo passerà in rassegna i principi base della tecnologia DDS e come specificare un CI DDS. Saranno introdotte poi alcune soluzioni di CI DDS adeguate e verrà spiegato come applicarle efficacemente.

Come funziona la sintesi digitale diretta

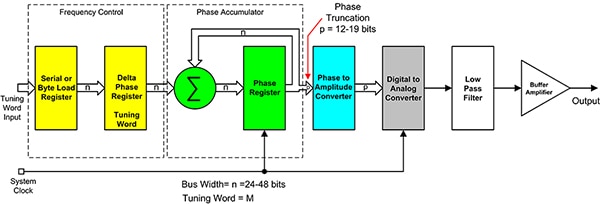

La sintesi digitale si basa su un accumulatore di fase che genera una serie di stati digitali, il cui valore aumenta linearmente formando una rampa numerica. Questo segnale è una funzione periodica in cui la fase istantanea della forma d'onda in uscita è un angolo espresso in radianti che varia nell'intervallo da zero a 2p. Questa è l'immissione digitale in una tabella di ricerca che converte la rampa numerica in un'onda sinusoidale (Figura 1). Anche se la più comune forma d'onda di uscita della tecnologia DDS è sinusoidale, sono facilmente generabili anche rampe, onde triangolari e quadre.

Figura 1: Il sintetizzatore digitale diretto si basa su un accumulatore di fase che genera la fase istantanea di una forma d'onda. Una tabella di ricerca fornisce la conversione fase-ampiezza che viene inviata a un convertitore digitale/analogico, producendo l'uscita analogica desiderata dopo il filtraggio. (Immagine per gentile concessione di DigiKey)

L'uscita della tabella di ricerca fase-ampiezza viene inviata a un convertitore digitale/analogico (DAC) e viene convertita in una forma d'onda analogica, normalmente sinusoidale. Dato che l'ingresso al DAC è costituito da una serie di valori campionati, l'uscita è espressa in fasce di quantizzazione. Queste fasce producono immagini spettrali indesiderate in multipli della frequenza di campionamento nel dominio della frequenza. Un filtro passa-basso, a valle del DAC, sopprime queste risposte spettrali indesiderate.

L'accumulatore di fase

L'accumulatore di fase è un contatore a modulo N i cui stati digitali 2N vengono incrementati per ogni ciclo di clock in ingresso nel sistema. La dimensione dell'incremento dipende dal valore della parola binaria programmabile, M, applicata al sommatore dell'accumulatore. La parola binaria fissa la dimensione del passo di incremento del contatore. Questo determinerà la frequenza della forma d'onda di uscita.

L'accumulatore di fase ha generalmente da 24 a 48 bit. A 24 bit ci sono 224 o 16.777.216 stati. Questo numero rappresenta il numero di valori di fase in radianti tra 0 e 2p o l'incremento di fase ottenibile. Per un accumulatore di fase a 24 bit, la risoluzione di fase è di 3,74 E-7 radianti. Se si utilizza un accumulatore di fase più grande, l'incremento di fase diventa ancora più fine.

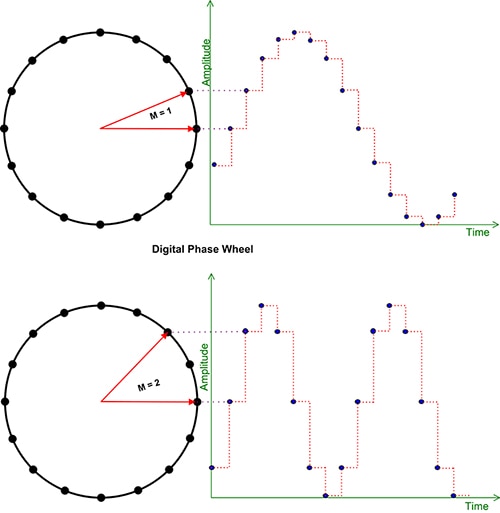

Un modo per visualizzare il funzionamento dell'accumulatore di fase è di pensarlo simile a una ruota di fase (Figura 2).

Figura 2: Una visualizzazione semplificata di un accumulatore a 16 stati di fase basata su una ruota di fase per spiegare come la parola binaria influisce sulla frequenza di uscita del DDS. (Immagine per gentile concessione di DigiKey)

Gli stati dell'accumulatore sono periodici e sono rappresentati disposti su un cerchio. I punti sul cerchio rappresentano tutti gli stati di fase dell'accumulatore. Nel caso illustrato, per semplicità, l'accumulatore ha 16 stati. Se la parola binaria è uguale a uno come nel diagramma in alto, allora l'incremento di passo ad ogni ciclo di clock è uno e, durante l'intero periodo, vengono selezionati tutti gli stati.

A destra della ruota di fase è riportata graficamente l'uscita analogica per ogni stato. Trattandosi di un dispositivo quantizzato, l'uscita analogica mantiene il suo stato corrente finché il clock non fa avanzare la ruota di fase al suo stato successivo. La forma d'onda di uscita è costituita da un singolo ciclo dell'onda sinusoidale quantizzata contenente sedici valori.

Nello schema sottostante, il valore della parola binaria è impostato su due. Con questa impostazione, viene selezionato ogni secondo stato della ruota di fase. L'uscita analogica è ora composta da due cicli, ciascuno con otto ampiezze, per un totale di sedici stati. Con la parola impostata su due, la frequenza di uscita è ora il doppio del valore ottenuto in precedenza.

La frequenza di uscita del DDS viene impostata dal valore della parola binaria e aumenta proporzionalmente a tale valore. La frequenza di campionamento rimane fissa alla frequenza di clock del sistema e l'intervallo di tempo tra i campioni in uscita è costante. La frequenza di uscita dipende dall'incremento del valore della parola binaria; all'aumento di questo valore diminuiscono i passi in ogni ciclo di uscita e cresce così la frequenza. La parola può essere aumentata fino a che non si hanno solo due campioni per ciclo, il che porta l'uscita DDS alla sua frequenza di Nyquist, ovvero la metà della frequenza di clock del sistema. In genere, il DDS è limitato progettualmente per avere sempre una frequenza di uscita inferiore al limite di Nyquist.

Oltre che dalla frequenza di clock del sistema, la frequenza di uscita del DDS dipende anche dal valore della parola binaria programmabile e dalla lunghezza dell'accumulatore. L'equazione 1 lo esemplifica:

![]() Equazione 1

Equazione 1

Dove:

fout è la frequenza di uscita del DDS

M è il valore della parola binaria programmabile

fc è la frequenza di clock del sistema

N è la lunghezza dell'accumulatore di fase

L'uscita dell'accumulatore di fase, che è la fase istantanea della forma d'onda in uscita, viene utilizzata per pilotare il convertitore fase-ampiezza. Il convertitore fase-ampiezza emette una parola digitale, il cui valore è l'ampiezza della forma d'onda sinusoidale per la fase di ingresso.

È bene notare che il numero di bit utilizzati per pilotare il convertitore fase-ampiezza è inferiore a quello utilizzato per l'accumulatore di fase. Viene detto troncamento della fase e serve a ridurre la dimensione della ROM e il consumo energetico degli stadi digitali dopo l'accumulatore di fase. Il troncamento dell’informazione di fase in uscita dall’accumulatore determina la presenza di spurie all’interno dello spettro d’uscita, che possono essere minimizzate con un'attenta progettazione.

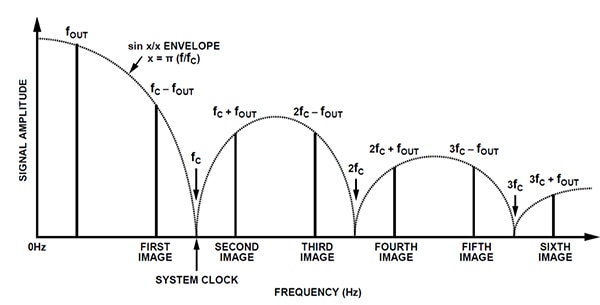

Perché inserire un filtro passa-basso in uscita

Le forme d'onda mostrate nella Figura 2 sono ricche di armoniche dovute alla conformazione a gradini. Di conseguenza, è necessario un filtro passa-basso per rimuovere queste armoniche dello spettro, così come altre risposte in frequenza spurie derivanti da altri processi all'interno del DDS.

Ad esempio, nella Figura 3 viene illustrato lo spettro di uscita del DDS per un dispositivo con clock fc con una frequenza di uscita inferiore a fc/2. Lo spettro di uscita mostra la linea spettrale di uscita, fout, con le sue repliche di frequenza (frequenza immagine) sopra e sotto la frequenza di clock, e tutte le sue armoniche fino alla terza e oltre.

Figura 3: Vista dello spettro di uscita di un DDS con una frequenza di clock di sistema fc e una frequenza di uscita fout in cui si evidenziano le componenti della frequenza di uscita fino alla terza armonica del clock. (Immagine per gentile concessione di Analog Devices)

La banda della frequenza di uscita del DDS è compresa tra 0 Hz e il limite di Nyquist a fc/2. La forma sin(x)/x è dovuta al segnale quantizzato nel dominio del tempo, come mostrato nella Figura 2. Gli zeri della funzione sin(x)/x si verificano alla frequenza di clock e a tutte le sue armoniche. È possibile applicare correzioni di ampiezza per annullare la forma sin(x)/x al fine di migliorare la planarità dell'ampiezza su tutto l'intervallo di uscita.

Per ridurre significativamente l'ampiezza delle componenti spettrali al di sopra della banda di Nyquist, viene applicato un filtro passa-basso con un taglio netto al di sopra del campo di frequenza del DDS. Se il campo di frequenza del DDS venisse esteso alla frequenza di Nyquist, il filtro richiederebbe una pendenza di taglio ripida e infinita per escludere la frequenza di immagine più bassa intorno alla frequenza di clock, che si sovrapporrebbe alla frequenza di Nyquist. Questa è una delle ragioni per cui il campo di frequenza del DDS è raramente esteso alla frequenza di Nyquist.

Progettazione con circuiti integrati DDS commerciali

Quando si seleziona e si utilizza un DDS, sono molti i fattori da prendere in considerazione. Anzitutto, occorre esaminare la funzionalità necessaria per le specifiche applicazioni, il campo di frequenza richiesto, l'ampiezza e la gamma di offset, la forma d'onda, la risoluzione e la capacità di modulazione. La purezza del segnale è generalmente un fattore di selezione per una sorgente di segnali. La gamma dinamica in assenza di spurie (SFDR), la distorsione armonica totale (THD) e il rumore di fase sono le specifiche chiave, così come il consumo energetico, specialmente nelle applicazioni mobili.

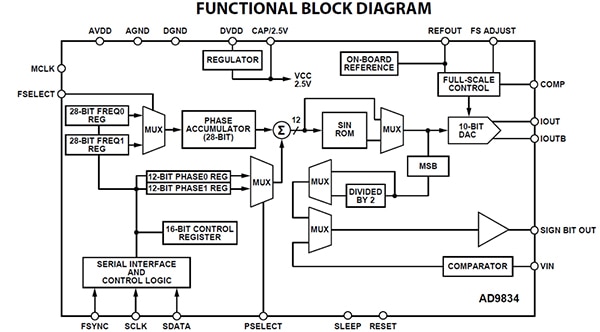

Un buon esempio di dispositivo a basso consumo è offerto dal DDS AD9834BRUZ-REEL7 di Analog Devices (Figura 4). Questo dispositivo è controllato da un'interfaccia seriale a tre fili e consuma solo 20 mW da un'alimentazione di 3 V. È in grado di produrre funzioni di onda sinusoidale, di rampa e quadra e ha una frequenza massima di clock di 50 MHz, mostrata in figura con l'MCLK come ingresso di clock digitale. Sulla base della precedente discussione su Nyquist, questa frequenza di clock significa che può emettere forme d'onda fino a 25 MHz.

Figura 4: Schema funzionale interno del DDS AD9834 a basso consumo di Analog Devices. Il dispositivo consuma 20 mW da un'alimentazione a 3 V e può produrre funzioni d'onda sinusoidale, di rampa e quadra fino a 25 MHz. (Immagine per gentile concessione di Analog Devices)

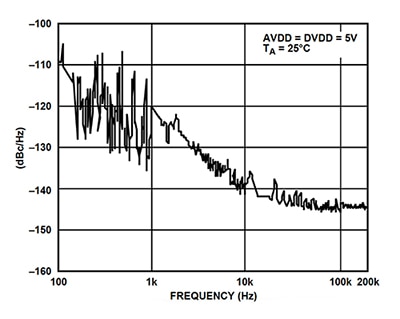

L'accumulatore di fase ha una lunghezza di 28 bit, per una risoluzione di frequenza di 0,186 Hz a una frequenza di clock di 50 MHz. Il rumore di fase dipende anche dalla qualità dell'ingresso dell'MCLK ed è mostrato come funzione di un offset dalla portante (Figura 5). Nel caso di AD9834, il rumore di fase è di -120 dBc/Hz con un offset di 1 kHz rispetto alla portante per un FOUT di 2 MHz e un MCLK di 50 MHz.

Figura 5: Il rumore di fase dipende dalla qualità dell'MCLK e viene mostrato come -120 dBc/Hz con un offset di 1 kHz dalla portante per un FOUT di 2 MHz e un MCLK di 50 MHz. (Immagine per gentile concessione di Analog Devices)

Il DAC integrato ha una risoluzione di 10 bit e l'SFDR a banda stretta è tipicamente migliore di -78 dB.

Le caratteristiche di AD9834 includono doppi registri di fase e frequenza per supportare sia la modulazione di frequenza che di fase. Inoltre, la memoria di sola lettura (ROM) sinusoidale può essere bypassata per pilotare il DAC utilizzando l'uscita dell'accumulatore di fase per produrre una funzione di rampa. Il bit di segno è disponibile su un pin di uscita per fornire un'onda quadra per la generazione di segnali di clock.

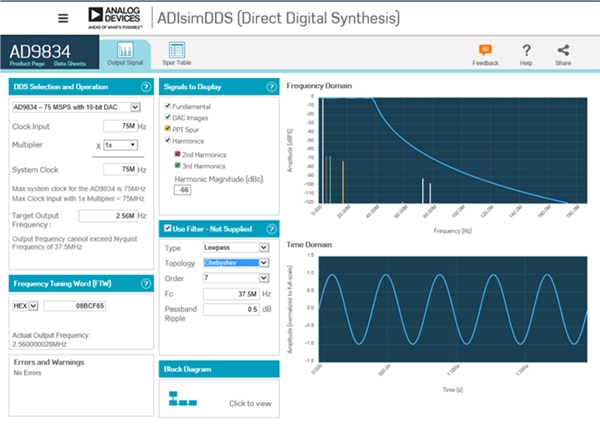

Per facilitare il processo di progettazione, spesso i fornitori offrono buoni strumenti di selezione. Il DDS AD9834 è supportato da ADIsimDDS di Analog Devices, uno strumento di progettazione interattivo online che consente ai progettisti di valutare varie configurazioni, tra cui frequenze di uscita, parole binarie programmabili e clock di riferimento (Figura 6).

Figura 6: Lo strumento di progettazione interattivo ADIsimDDS di Analog Devices consente ai progettisti di sperimentare varie configurazioni e opzioni di filtraggio. (Immagine per gentile concessione di Analog Devices)

Il programma ADIsimDDS inizia con la selezione di uno specifico prodotto DDS, in questo caso AD9834. L'utente inserisce la frequenza di clock del sistema e la frequenza di uscita desiderata, e il programma calcola la parola binaria per l'accumulatore di fase. Una vista del dominio della frequenza mostra lo spettro dell'uscita del DDS, inclusi il segnale di uscita, le armoniche, le immagini DAC, le armoniche e le immagini del clock. All'uscita del DDS può essere applicato un simulatore di filtri per vedere gli effetti dei vari filtri sullo spettro di uscita.

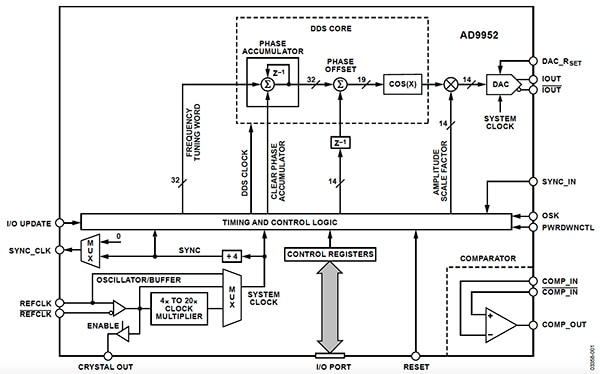

Se il progetto richiede prestazioni e frequenze più elevate, AD9952YSVZ-REEL7 di Analog Devices ha una frequenza massima di clock di 400 MHz e può produrre segnali sinusoidali fino a 200 MHz con rumore di fase inferiore e un SFDR specificato a >80 dB a 160 MHz (offset di ±100 kHz) AOUT. Confrontandolo direttamente con AD9834, il suo SFDR a banda stretta è tipicamente -70 dB a 20 MHz, ma ovviamente dipende dalla frequenza.

AD9952 non utilizza un ingresso MCLK. Ha invece un oscillatore di clock integrato con un moltiplicatore PLL associato che può moltiplicare il segnale per fattori da 4 a 20 volte utilizzando un singolo cristallo esterno (Figura 7). La presenza di un proprio clock di sistema interno (fino a 400 Msps) permette al DDS di ottenere il suo basso rumore di fase di ≤-120 dBc/Hz a un offset di 1 kHz.

Figura 7: AD9952 prende l'ingresso del cristallo esterno e genera il proprio clock interno di sistema per controllare meglio le condizioni necessarie per ottenere prestazioni superiori, come ad esempio un minor rumore di fase. (Immagine per gentile concessione di Analog Devices)

AD9952 dispone anche di un accumulatore di fase a 32 bit e di un DAC a 14 bit. Il DDS è controllato tramite interfaccia seriale.

Per una gamma di frequenze più ampia, Analog Devices mette a disposizione AD9957BSVZ-REEL, un dispositivo che supporta frequenze di clock fino a 1 GHz con frequenze di uscita fino a 400 MHz per applicazioni di comunicazione avanzate. Utilizzando un accumulatore di fase a 32 bit e un DAC ad alta velocità a 14 bit, questo dispositivo viene visto come un modulatore in quadratura e genera componenti sia in fase (I) che in quadratura (Q) controllati da otto registri di fase/frequenza. Questi sono utilizzati per produrre sull'uscita un flusso di dati modulato in quadratura. Per compensare la forma sin(x)/x discussa in precedenza, è disponibile un filtro SINC (sin(x)/x) inverso opzionale.

Questi sono tre esempi di circuiti integrati DDS disponibili in commercio che possono soddisfare compiti di generazione del segnale, da semplici a complessi.

Conclusione

Di fronte al continuo sforzo per migliorare le prestazioni, le dimensioni, i costi e il consumo energetico dei sistemi wireless, i progettisti possono trovare nei DDS una buona opzione. Portano stabilità digitale, agilità e ripetibilità alla generazione del segnale, offrendo forme d'onda in uscita multiple e capacità di modulazione avanzata, incluso il salto di frequenza e di fase. Dato che sono entrati nel ventaglio di prodotti adottati dai progettisti, i fornitori hanno pensato di semplificare anche la selezione e l'integrazione attraverso l'uso di strumenti avanzati che accorciano il processo di progettazione.

Esonero della responsabilità: le opinioni, le convinzioni e i punti di vista espressi dai vari autori e/o dai partecipanti al forum su questo sito Web non riflettono necessariamente le opinioni, le convinzioni e i punti di vista di DigiKey o le sue politiche.