Perché e come utilizzare gli FPGA di Efinix per l'imaging IA/ML - Parte 1: Primi passi

Contributo di Editori europei di DigiKey

2023-04-20

Nota del redattore: i nuovi approcci alle architetture FPGA offrono un controllo più preciso e una maggiore flessibilità per soddisfare le esigenze dell'apprendimento automatico (ML) e dell'intelligenza artificiale (IA). La prima parte di questa serie in due parti presenta una di queste architetture di Efinix e spiega come muovere i primi passi utilizzando una scheda di sviluppo. La seconda parte parlerà dell'interfacciamento della scheda di sviluppo con dispositivi e periferiche esterne, ad esempio una telecamera.

Gli FPGA svolgono un ruolo fondamentale in molte applicazioni, dal controllo industriale alla sicurezza, dalla robotica ai settori aerospaziale e automotive. Grazie alla flessibilità del core logico programmabile e alle loro ampie capacità di interfacciamento, un campo applicativo in crescita per gli FPGA riguarda l'elaborazione delle immagini quando si deve ricorrere all'inferenza ML. Gli FPGA sono ideali per l'implementazione di soluzioni con diverse interfacce per telecamere ad alta velocità. Inoltre, gli FPGA consentono di implementare nella logica pipeline di elaborazione dedicate, eliminando così i colli di bottiglia spesso associati alle soluzioni basate su CPU o GPU.

Per molti sviluppatori, tuttavia, le loro applicazioni richiedono un maggior numero di funzionalità ML/IA e un controllo più preciso del routing e della logica, al di là di quanto possano fornire le classiche architetture FPGA con blocchi logici combinatori (CLB). I nuovi approcci alle architetture FPGA affrontano questi problemi. Ad esempio, l'architettura Quantum di Efinix utilizza un blocco di logica e routing intercambiabile (XLR).

Questo articolo illustra le caratteristiche e gli attributi principali dell'architettura FPGA di Efinix, ne sottolinea le capacità IA/ML e presenta alcune implementazioni reali. Illustra quindi una scheda di sviluppo e gli strumenti associati che gli sviluppatori possono utilizzare per iniziare senza indugio un progetto di imaging IA/ML.

Dispositivi FPGA di Efinix

Efinix offre attualmente due gamme di dispositivi. Inizialmente ha presentato la famiglia Trion, che offre densità da 4000 a 120.000 elementi logici (LE) ed è prodotta con un processo SMIC 40LL. L'ultima linea di dispositivi, la famiglia Titanium, offre densità da 35.000 a 1 milione di elementi logici ed è prodotta sul diffusissimo nodo TSMC a 16 nm.

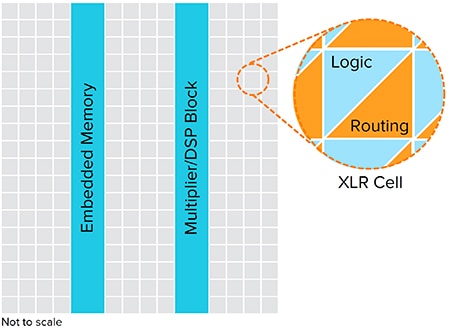

Entrambe le offerte si basano sull'architettura Quantum, unica nel mondo degli FPGA. L'architettura standard dell'FPGA si basa su CLB che, al livello più semplice, contengono una tabella di ricerca (LUT) e una serie di flip-flop. I CLB implementano equazioni logiche che vengono poi interconnesse tramite routing. L'architettura Quantum di Efinix si allontana dai blocchi di logica e routing distinti con il blocco XLR.

L'unicità di un blocco XLR sta nel fatto che può essere configurato per funzionare come una cella logica con una LUT, un registro e un sommatore o una matrice di routing. Questo approccio offre un'architettura più precisa per la flessibilità di routing, consentendo alle implementazioni pesanti dal punto di vista di logica o routing di ottenere le prestazioni desiderate.

Figura 1: L'unicità di un blocco XLR sta nel fatto che può essere configurato per funzionare come una cella logica con una LUT, un registro e un sommatore o una matrice di routing. (Immagine per gentile concessione di Efinix)

Figura 1: L'unicità di un blocco XLR sta nel fatto che può essere configurato per funzionare come una cella logica con una LUT, un registro e un sommatore o una matrice di routing. (Immagine per gentile concessione di Efinix)

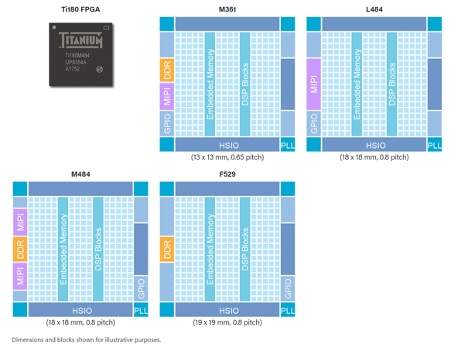

Essendo la famiglia più recente, i dispositivi Titanium offrono agli sviluppatori le funzioni più avanzate (Figura 2). Insieme al core XLR, forniscono collegamenti seriali multi-gigabit a 16 Gbps o 25,8 Gbps, a seconda del dispositivo scelto. Questi collegamenti multi-gigabit sono fondamentali per il trasferimento di dati ad alta velocità all'interno e all'esterno del chip.

Figura 2: L'FPGA Titanium Ti180 è disponibile in diverse opzioni a seconda della larghezza del bus, degli I/O e dei requisiti di memoria. (Immagine per gentile concessione di Efinix)

Figura 2: L'FPGA Titanium Ti180 è disponibile in diverse opzioni a seconda della larghezza del bus, degli I/O e dei requisiti di memoria. (Immagine per gentile concessione di Efinix)

I dispositivi Titanium offrono anche un'ampia gamma di funzionalità di interfacciamento di ingresso/uscita (I/O) che possono essere raggruppate come I/O per uso generale (GPIO) e che possono supportare standard di I/O a terminazione singola come CMOS a bassa tensione (LVCMOS) a 3,3 V, 2,5 V e 1,8 V.

Per l'interfacciamento differenziale e ad alta velocità, i dispositivi Titanium offrono I/O ad alta velocità (HSIO) che supporta standard di I/O a terminazione singola come LVCMOS a 1,2 V, 1,5 V, SSTL e HSTL. Gli standard di I/O differenziale supportati da HSIO includono la segnalazione differenziale a bassa tensione (LVDS), SSTL differenziale e HSTL.

I moderni FPGA richiedono anche una memoria strettamente accoppiata e ad alta larghezza di banda, utilizzata per memorizzare i fotogrammi per le applicazioni di elaborazione delle immagini, i dati di campionamento per l'elaborazione dei segnali e, naturalmente, per eseguire i sistemi operativi e il software per i processori implementati all'interno dell'FPGA. La gamma di dispositivi Titanium offre la possibilità di interfacciarsi con Dynamic Data Rate 4 (DDR4) e con DDR4(x) a basso consumo (LPDDR4(x)). A seconda del dispositivo Titanium selezionato, la larghezza di bus supportata è x32 (J) o x16 (M); alcuni dispositivi non supportano LPDDR4 (L).

Gli FPGA Titanium si basano su SRAM e richiedono una memoria di configurazione; la configurazione del dispositivo può essere eseguita tramite interconnessione periferica seriale (SPI) master/slave o JTAG. Per garantire la sicurezza di questo metodo di configurazione, l'FPGA Titanium utilizza la crittografia AES GCM del bitstream, oltre a AES GCM e RSA-4096 per l'autenticazione del bitstream. Un tale elevato livello di sicurezza è necessario dal momento che gli FPGA sono distribuiti all'edge, dove possibili malintenzionati potrebbero accedervi e manipolarne il comportamento.

Introduzione alla scheda di sviluppo

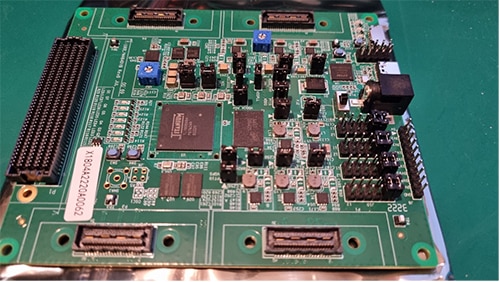

Le schede di sviluppo sono un elemento critico del processo di valutazione degli FPGA, in quanto possono essere utilizzate per esplorare le capacità di un dispositivo e prototipare applicazioni, contribuendo così a ridurre il rischio complessivo. La prima scheda di sviluppo disponibile per valutare gli FPGA Titanium e iniziare la prototipazione di applicazioni è il modello Ti180 M484 (Figura 3). La scheda dispone di un connettore per scheda mezzanine FPGA (FMC) e di quattro connettori QSE di Samtec.

Figura 3: Oltre a un FPGA Titanium, il kit di sviluppo Ti180 M484 presenta un connettore FMC e quattro connettori QSE di Samtec. (Immagine per gentile concessione di Adam Taylor)

Figura 3: Oltre a un FPGA Titanium, il kit di sviluppo Ti180 M484 presenta un connettore FMC e quattro connettori QSE di Samtec. (Immagine per gentile concessione di Adam Taylor)

L'FPGA Ti180 montato su questa scheda di sviluppo fornisce 172K celle XLR, 32 clock globali, 640 elementi di elaborazione del segnale digitale (DSP) e 13 Mbit di RAM embedded. Gli elementi DSP consentono di implementare moltiplicazioni 18 x 19 in virgola fissa e moltiplicazioni a 48 bit. Questo DSP può anche essere ottimizzato per operazioni a istruzioni singole e dati multipli (SIMD) in configurazione doppia o quadrupla. Gli elementi DSP possono anche essere configurati per eseguire operazioni in virgola mobile.

Come la maggior parte delle schede di sviluppo, Ti180 offre semplici LED e pulsanti. La sua vera forza, tuttavia, risiede nelle sue capacità di interfacciamento. La scheda di sviluppo Ti180 dispone di un connettore FMC a basso piedinatura che consente di collegare un'ampia gamma di periferiche. Essendo uno standard molto diffuso, esistono molte schede FMC per l'interfacciamento di convertitori analogico/digitale (ADC) ad alta velocità, convertitori digitale/analogico (DAC), reti e soluzioni di memoria/storage.

Oltre alla connessione FMC, la scheda dispone di quattro connettori QSE di Samtec con cui lo sviluppatore può aggiungere schede di espansione. Questi connettori QSE sono utilizzati per fornire ingressi e uscite MIPI; ogni connettore QSE fornisce un ingresso o un'uscita MIPI.

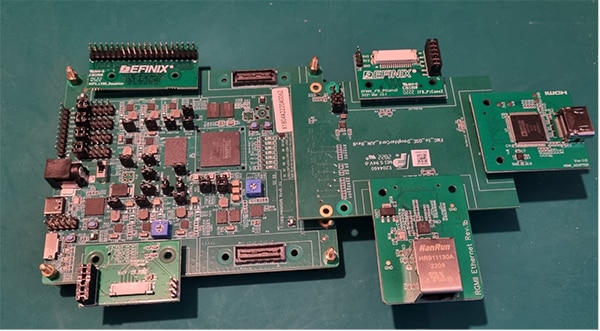

Figura 4: Kit di sviluppo Ti180 M484 con la versatile gamma di opzioni di espansione basate su connettori QSE e FMC. (Immagine per gentile concessione di Adam Taylor)

Figura 4: Kit di sviluppo Ti180 M484 con la versatile gamma di opzioni di espansione basate su connettori QSE e FMC. (Immagine per gentile concessione di Adam Taylor)

La scheda Ti180 offre anche 256 Mbit di LPDDR4 per supportare la memoria ad alte prestazioni necessaria nelle applicazioni di elaborazione di immagini e segnali. Inoltre, la scheda di sviluppo offre una gamma di opzioni di clock a 25, 33,33, 50 e 74,25 MHz, utile per generare diverse frequenze interne con il circuito ad aggancio di fase (PLL) del dispositivo.

La possibilità di riprogrammare e di eseguire il debug in tempo reale sulla scheda durante lo sviluppo è fondamentale e richiede una connessione JTAG, fornita tramite un'interfaccia USB-C su scheda. Viene inoltre fornita una memoria non volatile sotto forma di due dispositivi NOR flash da 256 Mbit che possono essere utilizzati per dimostrare la soluzione di configurazione.

La scheda è alimentata da un adattatore universale da 12 V incluso nella confezione. È inoltre inclusa una scheda di breakout da FMC a QSE, oltre a schede di espansione basate su QSE per HDMI, Ethernet, MIPI e LVDS. Per dimostrare le capacità di elaborazione delle immagini di Ti180, sono anche disponibili una scheda figlia RPI doppia e due schede telecamera IMX477.

Ambiente software

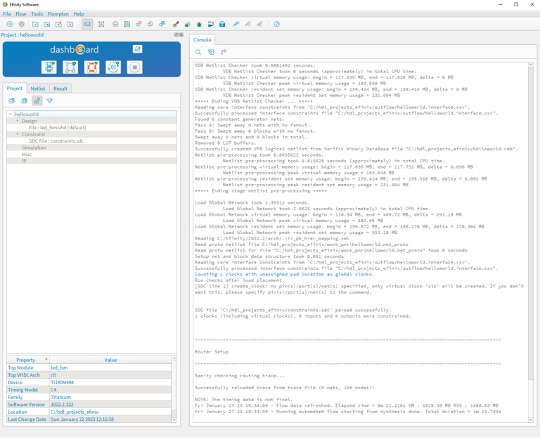

Per l'implementazione di progetti destinati alla scheda di sviluppo Ti180 si utilizza il software Efinity di Efinix. Questo software consente di generare un flusso di bit tramite sintesi e place-and-route. Inoltre, fornisce agli sviluppatori blocchi di proprietà intellettuale (IP), analisi dei tempi e debug su chip.

Per accedere al software Efinity è necessario disporre di una scheda di sviluppo. A differenza di altri fornitori, però, lo strumento non ha versioni diverse che richiedono licenze aggiuntive.

Con Efinity si creano nuovi progetti per il dispositivo selezionato. È quindi possibile aggiungere al progetto i file RTL e creare i vincoli per la temporizzazione e la progettazione degli I/O. È all'interno di Efinity che gli sviluppatori possono anche implementare il design dell'I/O, utilizzando HSIO, GPIO e I/O specializzato.

Figura 5: In Efinity si creano nuovi progetti per il dispositivo selezionato. (Immagine per gentile concessione di Adam Taylor)

Figura 5: In Efinity si creano nuovi progetti per il dispositivo selezionato. (Immagine per gentile concessione di Adam Taylor)

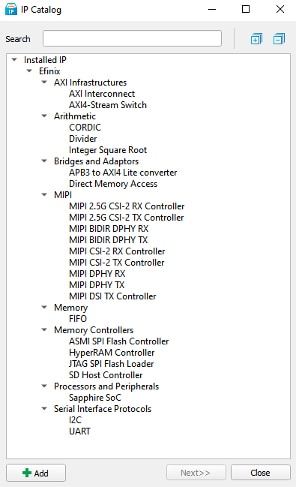

Un elemento critico della progettazione di FPGA è lo sfruttamento dell'IP, soprattutto per IP complessi come le interconnessioni AXI, i controller di memoria e i processori softcore. Efinity mette a disposizione una serie di blocchi IP che possono essere utilizzati per accelerare la progettazione.

Figura 6: Efinity fornisce agli sviluppatori un catalogo di IP utile per accelerare la progettazione. (Immagine per gentile concessione di Adam Taylor)

Figura 6: Efinity fornisce agli sviluppatori un catalogo di IP utile per accelerare la progettazione. (Immagine per gentile concessione di Adam Taylor)

Sebbene gli FPGA siano eccellenti nell'implementazione di strutture di elaborazione parallela, molti progetti di FPGA includono processori softcore, che consentono di implementare l'elaborazione sequenziale, come le comunicazioni di rete. Per l'implementazione dei processori softcore nei dispositivi Efinix, Efinity fornisce lo strumento di configurazione del System-on-Chip (SoC) Sapphire. Con Sapphire lo sviluppatore può definire un sistema multiprocessore dotato di cache e coerenza cache su più processori, oltre a eseguire un sistema operativo Linux incorporato. All'interno di Sapphire, lo sviluppatore può scegliere tra uno e quattro processori softcore.

Il processore softcore implementato è la soft CPU VexRiscV, basata sull'architettura RISC-V. Il processore VexRiscV è un'implementazione a 32 bit che dispone di estensioni pipeline e offre un set di funzionalità configurabili che lo rendono ideale per l'implementazione nei dispositivi di Efinix. Le configurazioni opzionali includono un moltiplicatore, istruzioni atomiche, estensioni in virgola mobile e istruzioni compresse. A seconda della configurazione del sistema SoC, le prestazioni saranno comprese tra 0,86 e 1,05 DMIPS/MHz.

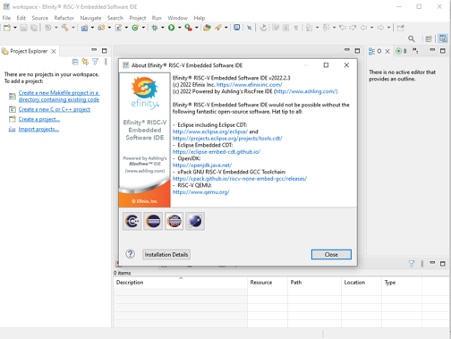

Una volta progettato e implementato l'ambiente hardware nel dispositivo di Efinix, il software applicativo può essere sviluppato utilizzando l'IDE Ashling RiscFree. Ashling RiscFree è un IDE basato su Eclipse per la creazione e la compilazione di software applicativo, nonché il debug sul target per mettere a punto l'applicazione prima della distribuzione.

Figura 7: Ashling RiscFree è un IDE basato su Eclipse per la creazione e la compilazione di software applicativo e il debug sul target. (Immagine per gentile concessione di Adam Taylor)

Figura 7: Ashling RiscFree è un IDE basato su Eclipse per la creazione e la compilazione di software applicativo e il debug sul target. (Immagine per gentile concessione di Adam Taylor)

Se si sviluppa una soluzione Linux embedded, vengono forniti tutti gli artefatti di avvio necessari, compresi First Stage Boot Loader, OpenSBI, U-Boot e Linux con Buildroot. In alternativa, lo sviluppatore può utilizzare FreeRTOS per una soluzione in tempo reale.

Implementazione IA

L'implementazione dell'intelligenza artificiale di Efinix si basa sul funzionamento del softcore RISC-V. Questo sfrutta la capacità di istruzione personalizzata del processore RISC-V per l'accelerazione delle soluzioni TensorFlow Lite. L'uso del processore RISC-V consente inoltre agli utenti di creare istruzioni personalizzate che possono essere utilizzate come parte della pre-elaborazione o della post-elaborazione successiva all'inferenza IA, creando una soluzione più reattiva e deterministica.

Per iniziare un'implementazione IA, si inizia esplorando lo zoo di modelli di Efinix, una libreria di modelli IA/ML ottimizzati per la tecnologia finale. Per gli sviluppatori che lavorano con i dispositivi di Efinix, è possibile accedere allo zoo dei modelli e addestrare la rete utilizzando Jupyter Notebooks o Google Colab. Una volta addestrata, la rete può essere convertita da un modello in virgola mobile a uno quantizzato utilizzando il convertitore TensorFlow Lite.

Dopo aver ottenuto il formato TensorFlow Lite, con l'acceleratore tinyML di Efinix si può creare una soluzione implementabile sulla soluzione RISC-V. Con il generatore tinyML lo sviluppatore può personalizzare l'implementazione dell'acceleratore e generare i file di progetto. Se distribuita in questo modo, l'accelerazione può essere da 4 a 200 volte superiore, a seconda dell'architettura e della personalizzazione scelte.

Conclusione

I dispositivi di Efinix offrono agli sviluppatori grande flessibilità grazie all'esclusiva architettura XLR. La toolchain offre la possibilità di implementare non solo progetti RTL, ma anche soluzioni SoC complesse che impiegano processori RISC-V softcore. Il SoC softcore è dotato di una soluzione IA/ML per l'implementazione dell'inferenza ML.

Esonero della responsabilità: le opinioni, le convinzioni e i punti di vista espressi dai vari autori e/o dai partecipanti al forum su questo sito Web non riflettono necessariamente le opinioni, le convinzioni e i punti di vista di DigiKey o le sue politiche.