Perché e come utilizzare gli FPGA di Efinix per l'imaging IA/ML Parte 2: Acquisizione ed elaborazione delle immagini

Contributo di Editori europei di DigiKey

2023-05-05

Nota del redattore: i nuovi approcci alle architetture FPGA offrono un controllo più preciso e una maggiore flessibilità per soddisfare le esigenze dell'apprendimento automatico (ML) e dell'intelligenza artificiale (IA). La prima parte di questa serie in due parti presenta una di queste architetture di Efinix e spiega come muovere i primi passi utilizzando una scheda di sviluppo. Questa seconda parte illustra l'interfacciamento della scheda di sviluppo con dispositivi e periferiche esterne, ad esempio una telecamera e spiega come sfruttare un FPGA per eliminare i colli di bottiglia nell'elaborazione delle immagini.

Gli FPGA svolgono un ruolo fondamentale in molte applicazioni, dal controllo industriale alla sicurezza, dalla robotica ai settori aerospaziale e automotive. Grazie alla flessibilità del core logico programmabile e alle loro ampie capacità di interfacciamento, un campo applicativo in crescita per gli FPGA riguarda l'elaborazione delle immagini laddove si può impiegare l'apprendimento automatico (ML). Gli FPGA sono ideali per l'implementazione di soluzioni con diverse interfacce per telecamere ad alta velocità grazie alla loro struttura di logica parallela. Inoltre, gli FPGA consentono di utilizzare una pipeline di elaborazione dedicata nella logica, eliminando così i colli di bottiglia legati alla condivisione delle risorse spesso associati alle soluzioni basate su CPU o GPU.

Questo secondo sguardo agli FPGA Titanium di Efinix esaminerà l'applicazione di elaborazione delle immagini di riferimento fornita con la relativa scheda di sviluppo Ti180 M484. L'obiettivo è quello di comprendere gli elementi costitutivi del progetto e di identificare i punti in cui la tecnologia FPGA consente di eliminare i colli di bottiglia o di offrire altri vantaggi agli sviluppatori.

Progetto di riferimento basato su Ti180 M484

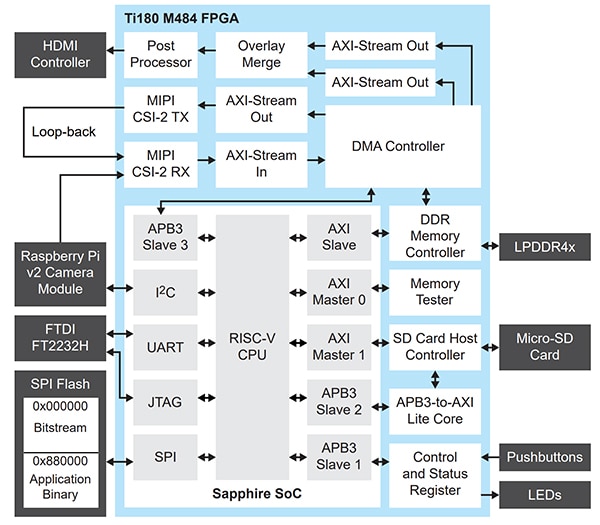

Concettualmente, il progetto di riferimento (Figura 1) riceve immagini da diverse telecamere MIPI (interfaccia di processore industriale mobile), esegue il buffering dei fotogrammi in LPDDR4x e quindi invia le immagini a un display HDMI (interfaccia multimediale ad alta definizione. Una scheda mezzanine FPGA (FMC) e quattro interfacce QSE di Samtec sulla scheda forniscono gli ingressi della telecamera e l'uscita HDMI.

Figura 1: Concettualmente, il progetto di riferimento Ti180 M484 riceve immagini da diverse telecamere MIPI, esegue il buffering dei fotogrammi in LPDDR4x e quindi invia le immagini a un display HDMI. >(Immagine per gentile concessione di Efinix)

Figura 1: Concettualmente, il progetto di riferimento Ti180 M484 riceve immagini da diverse telecamere MIPI, esegue il buffering dei fotogrammi in LPDDR4x e quindi invia le immagini a un display HDMI. >(Immagine per gentile concessione di Efinix)

La scheda di espansione da FMC a QSE viene utilizzata insieme alla scheda figlia HDMI come percorso video di uscita, mentre i tre connettori QSE servono per l'interfaccia con le telecamere MIPI SEN0494 di DFRobot. Se non sono disponibili più telecamere MIPI, è possibile utilizzare una singola telecamera eseguendo ciclicamente il canale della telecamera singola per simulare altre telecamere.

A un primo sguardo, questa applicazione può sembrare semplice. Tuttavia, la ricezione di più flussi MIPI ad alta definizione (HD) con una frequenza di fotogrammi elevata è una sfida. In questo caso la tecnologia FPGA è vantaggiosa perché consente ai progettisti di utilizzare più flussi MIPI in parallelo.

L'architettura del progetto di riferimento sfrutta strutture di elaborazione sia parallele sia sequenziali con l'FPGA. Le strutture parallele sono utilizzate per implementare la pipeline di elaborazione delle immagini, mentre un processore RISC-V fornisce l'elaborazione sequenziale utilizzata per le tabelle di ricerca (LUT) dell'FPGA.

In molti sistemi di elaborazione delle immagini basati su FPGA, la pipeline di elaborazione delle immagini può essere suddivisa in due elementi: il flusso di ingresso e quello di uscita. Il flusso di ingresso viene collegato all'interfaccia telecamera/sensore e le funzioni di elaborazione sono applicate all'uscita del sensore. Queste possono includere la conversione Bayer, il bilanciamento automatico del bianco e altri miglioramenti. Nel flusso di uscita, l'immagine viene preparata per la visualizzazione. Ciò include la modifica degli spazi colorimetrici (ad esempio, da RGB a YUV) e la post-elaborazione per il formato di uscita desiderato, ad esempio HDMI.

Spesso la catena di elaborazione dell'immagine in ingresso funziona alla velocità di clock dei pixel del sensore. La tempistica è diversa da quella della catena di uscita, che viene elaborata alla frequenza del display di uscita.

Per collegare l'ingresso alla pipeline di elaborazione dell'uscita viene utilizzato un buffer di fotogrammi, spesso conservato in una memoria esterna ad alte prestazioni, come LPDDR4x. Questo buffer si disaccoppia tra le pipeline di ingresso e di uscita per consentire l'accesso diretto alla memoria alla frequenza di clock appropriata.

Il progetto di riferimento Ti180 utilizza un approccio simile ai concetti sopra descritti. La pipeline di elaborazione delle immagini in ingresso implementa un core di proprietà intellettuale (IP) del ricevitore MIPI Camera Serial Interface 2 (CSI-2), costruito sullo strato fisico MIPI (MIPI D-PHY) con capacità di ingresso/uscita (I/O) dell'FPGA Titanium. MIPI è un'interfaccia impegnativa, perché utilizza segnali sia sbilanciati che differenziali sulla stessa coppia differenziale, oltre a comunicazioni a bassa e alta velocità. L'integrazione di MIPI D-PHY all'interno dell'I/O dell'FPGA riduce la complessità della scheda circuitale e la distinta base.

Una volta ricevuto il flusso di immagini dalla telecamera, il progetto di riferimento converte l'uscita MIPI CSI-2 RX in un flusso Advanced eXtensible Interface (AXI), un'interfaccia unidirezionale ad alta velocità che fornisce un flusso di dati da un master a uno slave. Sono previsti segnali di handshake per il trasferimento tra master e slave (tvalid e tready) e segnali in banda laterale. Questi segnali in banda laterale possono essere utilizzati per trasmettere informazioni sulla temporizzazione dell'immagine, come l'inizio del fotogramma e la fine della riga.

AXI Stream è ideale per le applicazioni di elaborazione delle immagini e consente a Efinix di fornire una serie di IP per l'elaborazione delle immagini facilmente integrabili nella catena di elaborazione come richiesto dall'applicazione.

Dopo la ricezione, i dati dell'immagine MIPI CSI-2 e i segnali di temporizzazione vengono convertiti in un flusso AXI e inseriti in un modulo di accesso diretto alla memoria (DMA), che scrive il fotogramma dell'immagine in LPDDR4x e funge da buffer di fotogrammi.

Questo modulo DMA opera sotto il controllo del core RISC-V nell'FPGA all'interno di un System-on-Chip (SoC) Sapphire. Questo SoC fornisce il controllo, come l'inizio e la fine delle scritture DMA, oltre a fornire al canale di scrittura DMA le informazioni necessarie per scrivere correttamente i dati dell'immagine in LPDDR4x, incluse le informazioni sulla posizione di memoria e sulla larghezza e altezza dell'immagine, definite in byte.

Il canale di uscita del progetto di riferimento legge le informazioni sull'immagine dal buffer di fotogrammi LPDDR4x sotto il controllo del SoC RISC-V. I dati sono emessi dall'IP DMA come flusso AXI, poi convertito dal formato RAW fornito dal sensore al formato RGB (Figura 2) e preparato per l'uscita tramite il trasmettitore HDMI ADV7511 di Analog Devices.

Figura 2: Immagini campione prodotte dal progetto di riferimento. (Immagine per gentile concessione di Adam Taylor)

Figura 2: Immagini campione prodotte dal progetto di riferimento. (Immagine per gentile concessione di Adam Taylor)

L'uso del DMA consente inoltre al SoC RISC-V Sapphire di accedere alle immagini memorizzate nel buffer di fotogrammi, alle statistiche astratte e alle informazioni sulle immagini. Il SoC Sapphire è anche in grado di scrivere overlay in LPDDR4x per unirli al flusso video in uscita.

I moderni sensori di immagine CMOS (CIS) hanno diverse modalità di funzionamento e possono essere configurati per fornire l'elaborazione su chip e diversi formati di uscita e schemi di clock. Questa configurazione è normalmente fornita tramite un'interfaccia I²C. Nel progetto di riferimento di Efinix, la comunicazione I²C con le telecamere MIPI è fornita dal processore SoC RISC-V Sapphire.

L'integrazione del processore RISC-V all'interno dell'FPGA Titanium riduce le dimensioni complessive della soluzione finale, in quanto elimina la necessità di implementare complesse macchine a stati dell'FPGA, che aumentano il rischio di progettazione, e processori esterni che allungano la distinta base.

L'inclusione del processore consente anche il supporto di un IP aggiuntivo per la comunicazione con la scheda MicroSD. Ciò consente di realizzare applicazioni reali in cui può essere necessario memorizzare le immagini per l'analisi successiva.

Nel complesso, l'architettura del progetto di riferimento Ti180 è ottimizzata per fornire una soluzione compatta, a basso costo e ad alte prestazioni con cui gli sviluppatori possono ridurre il costo in distinta base attraverso l'integrazione del sistema.

Uno dei vantaggi principali dei progetti di riferimento è che possono essere utilizzati per avviare lo sviluppo di applicazioni su hardware personalizzato, così che gli sviluppatori possano prendere gli elementi critici del progetto e personalizzarli come necessario. Ciò include la possibilità di utilizzare il flusso TinyML di Efinix per implementare applicazioni TinyML basate sulla visione che si eseguono sull'FPGA. In questo modo è possibile sfruttare sia la natura parallela della logica FPGA sia la capacità di aggiungere facilmente istruzioni personalizzate nei processori RISC-V, per creare acceleratori all'interno della logica FPGA.

Implementazione

Come illustrato nella Parte 1, l'architettura di Efinix è unica nel suo genere in quanto utilizza celle XLR (eXchangeable Logic and Routing) per fornire funzionalità di routing e di logica. Un sistema video come il progetto di riferimento è un sistema misto logico e di routing: è necessaria una logica estesa per implementare le funzioni di elaborazione delle immagini e un routing esteso per collegare le celle IP alle frequenze richieste.

Il progetto di riferimento utilizza circa il 42% delle celle XLR all'interno del dispositivo, lasciando ampio spazio per le aggiunte, comprese le applicazioni personalizzate come l'apprendimento automatico sull'edge.

Anche l'uso della RAM a blocchi e dei blocchi di elaborazione di segnali digitali (DSP) è molto efficiente, in quanto utilizza solo 4 dei 640 blocchi DSP e il 40% dei blocchi di memoria (Figura 3).

|

Figura 3: L'allocazione delle risorse sull'architettura di Efinix mostra che viene utilizzato solo il 42% delle celle XLR, lasciando ampio spazio per ulteriori processi. (Immagine per gentile concessione di Adam Taylor)

Nell'I/O del dispositivo, l'interfaccia DDR per LPDDR4x serve per fornire la memoria applicativa del SoC Sapphire e i buffer di fotogrammi delle immagini. Tutte le risorse MIPI dedicate al dispositivo sono utilizzate insieme al 50% dei circuiti ad aggancio di fase (Figura 4).

|

Figura 4: Istantanea dell'interfaccia e delle risorse di I/O utilizzate. (Immagine per gentile concessione di Adam Taylor)

L'I/O per uso generale (GPIO) è utilizzato per fornire le comunicazioni I²C e diverse interfacce collegate al SoC Sapphire, tra cui NOR flash, USB UART e scheda SD. HSIO viene utilizzato per fornire l'uscita video ad alta velocità al trasmettitore HDMI ADC7511.

Uno degli elementi cruciali della progettazione con FPGA non è solo l'implementazione e l'adattamento del progetto all'interno dell'FPGA, ma anche la capacità di posizionare il progetto logico all'interno dell'FPGA e di ottenere le prestazioni di temporizzazione richieste durante il routing.

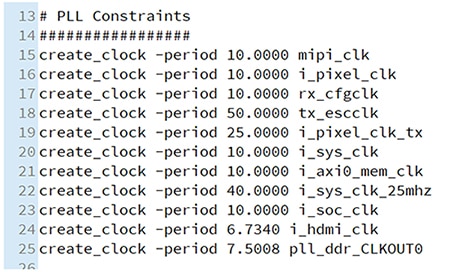

Sono ormai lontani i tempi dei progetti FPGA a singolo dominio di clock. Nel progetto di riferimento Ti180 sono presenti diversi clock, tutti ad alta frequenza. La tabella finale di temporizzazione mostra le frequenze massime raggiunte dai clock all'interno del sistema. Le prestazioni di temporizzazione richieste sono visibili anche nei vincoli (Figura 5), che prevedono una frequenza di clock massima di 148,5 MHz per il clock di uscita HDMI.

Figura 5: Vincoli di clock per il progetto di riferimento. (Immagine per gentile concessione di Adam Taylor)

Figura 5: Vincoli di clock per il progetto di riferimento. (Immagine per gentile concessione di Adam Taylor)

L'implementazione della temporizzazione rispetto ai vincoli mostra il potenziale della struttura XLR dell'FPGA Titanium, in quanto riduce il possibile ritardo di routing, aumentando così le prestazioni del progetto (Figura 6).

|

Figura 6: L'implementazione della temporizzazione rispetto ai vincoli mostra il potenziale della struttura XLR dell'FPGA Titanium per ridurre il possibile ritardo di routing, aumentando così le prestazioni del progetto. (Immagine per gentile concessione di Adam Taylor)

Conclusione

Il progetto di riferimento Ti180 M484 mostra chiaramente le capacità degli FPGA di Efinix e di Ti180 in particolare. Il progetto sfrutta diverse strutture di I/O uniche per implementare un complesso percorso di elaborazione delle immagini che supporta diversi flussi MIPI in ingresso. Questo sistema di elaborazione delle immagini opera sotto il controllo di un SoC soft-core Sapphire, che implementa gli elementi di elaborazione sequenziale necessari dell'applicazione.

Esonero della responsabilità: le opinioni, le convinzioni e i punti di vista espressi dai vari autori e/o dai partecipanti al forum su questo sito Web non riflettono necessariamente le opinioni, le convinzioni e i punti di vista di DigiKey o le sue politiche.