Abilitazione dell'interfaccia SSD NVMe su un kit di valutazione ZCU102 di Xilinx

Contributo di Editori nordamericani di DigiKey

2020-05-12

Panoramica

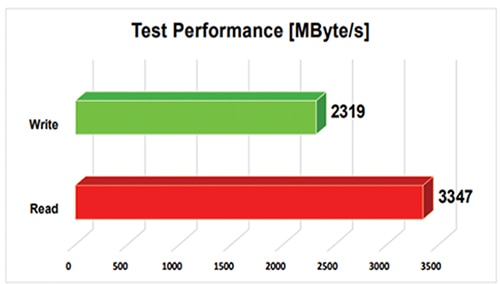

La famiglia di MPSoC Zynq® UltraScale+™, basata sull'architettura MPSoC UltraScale™ di Xilinx®, integra in un singolo dispositivo un sistema di elaborazione (PS) quad core o dual core a 64 bit basato su ARM, ricco di funzionalità e un'architettura UltraScale a logica programmabile (PL) di Xilinx. Include anche memoria su chip, interfacce di memoria esterna multiporta e un ricco set di interfacce di connettività periferiche, in particolare un transceiver GTH a 16,3 Gbps in grado di supportare un'interfaccia per dispositivi di memorizzazione PCI Express® Gen3 come un'unità SSD NVMe. Questo articolo presenta la soluzione di implementazione dell'interfaccia SSD (unità disco a stato solido) NVMe nel kit di valutazione ZCU102 di Xilinx utilizzando il core NVMeG3-IP di Design Gateway capace di raggiungere prestazioni incredibilmente elevate pari a 2319 MB/s in scrittura e 3347 MB/s in lettura.

Presentazione del kit di valutazione ZCU102 di MPSoC Zynq® UltraScale+

ZCU102 è una scheda di valutazione per uso generale per la prototipazione rapida basata sul dispositivo MPSoC XCZU9EG-2FFVB1156E. Include una SODIMM DDR4 ad alta velocità e interfacce di memoria per componenti, porte di espansione FMC, transceiver seriali da multi-gigabit al secondo, diverse interfacce periferiche e una logica FPGA per progetti personalizzabili. Questa combinazione permette di avere una piattaforma di prototipazione flessibile.

Figura 1: Kit di valutazione ZCU102 (Immagine per gentile concessione di Xilinx Inc.)

Figura 1: Kit di valutazione ZCU102 (Immagine per gentile concessione di Xilinx Inc.)

ZCU102 offre capacità di logica programmabile per realizzare applicazioni allo stato dell'arte come 5G Wireless, sistemi avanzati di assistenza alla guida (ADAS) di ultima generazione e soluzioni Internet delle cose industriale (IIoT).

In ogni caso, per l'applicazione che richiede un'archiviazione esterna dei dati ad alte prestazioni ed elevata affidabilità come le unità SSD NVMe, serve una soluzione idonea che sfrutti il transceiver GTH per la conformità all'interfaccia PCI Express® Gen3.

Introduzione all'unità di memorizzazione SSD NVMe

NVM Express (NVMe) definisce l'interfaccia per l'accesso del controller host come SSD tramite PCI Express. NVM Express ottimizza l'invio del comando e il processo di completamento utilizzando solo due registri (invio del comando e completamento del comando). Per il resto, NVMe supporta il funzionamento in parallelo gestendo fino a 64.000 comandi all'interno di una singola coda. I 64.000 comandi migliorano le prestazioni di trasferimento per l'accesso sia sequenziale che casuale.

Le unità NVMe hanno aperto la strada alla memorizzazione dei dati e al calcolo ad altissima velocità. Grazie alla tecnologia PCIe Express® Gen3, le moderne unità SSD NVMe possono raggiungere 40 Gbit/s.

Qui viene presentato un esempio di dispositivo di memorizzazione NVMe.

Implementazione del controller host NVMe su ZCU102

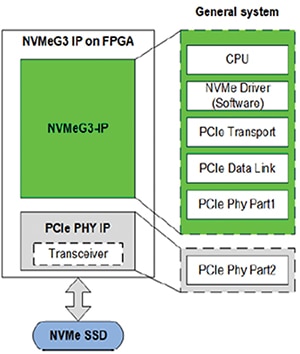

Figura 2: Implementazione di NVMe. (Immagine per gentile concessione di Design Gateway)

Figura 2: Implementazione di NVMe. (Immagine per gentile concessione di Design Gateway)

Tradizionalmente, l'host NVMe viene implementato utilizzando un processore host che opera con un controller PCIe per trasferire i dati da e verso l'SSD NVMe. Il protocollo NVMe è implementato per le comunicazioni dei driver dei dispositivi con la periferica CPU hardware del controller PCIe collegata per mezzo di un bus ad altissima velocità. Per il buffering dei dati e la coda dei comandi è richiesta una memoria DDR esterna per trasferire i dati tra il controller PCIe e SSD.

Dato che in ZCU102 non è disponibile un blocco integrato PCIe Gen3 su un dispositivo FPGA XCZU9EG-2FFVB1156E, non è possibile un approccio di implementazione convenzionale.

Design Gateway propone una soluzione utilizzando il Core NVMeG3-IP, come mostrato nella Figura 2, per abilitare un'interfaccia SSD NVMe per un dispositivo MPSoC Zynq® UltraScale+™ per il quale non è disponibile un blocco integrato PCIe. L'interfaccia NVMe per ZCU102 consente di realizzare un sistema RAID multicanale con prestazioni molto elevate e un consumo molto basso di risorse FPGA. La licenza del core NVMeG3-IP include il progetto di riferimento di esempio che aiuta i progettisti a ridurre i tempi e i costi di sviluppo.

Panoramica di NVMeG3-IP di Design Gateway

Il core NVMe IP con PCIe Gen3 Soft IP (NVMeG3-IP) è ideale per accedere a SSD NVMe senza blocco integrato PCIe, CPU e memoria esterna. NVMeG3-IP include PCIe Gen3 Soft IP e 256 kB di memoria. Questa soluzione è consigliata per l'applicazione che richiede un'unità di memorizzazione SSD NVMe con prestazioni ad altissima velocità utilizzando un FPGA a basso costo che non contiene un blocco integrato PCIe.

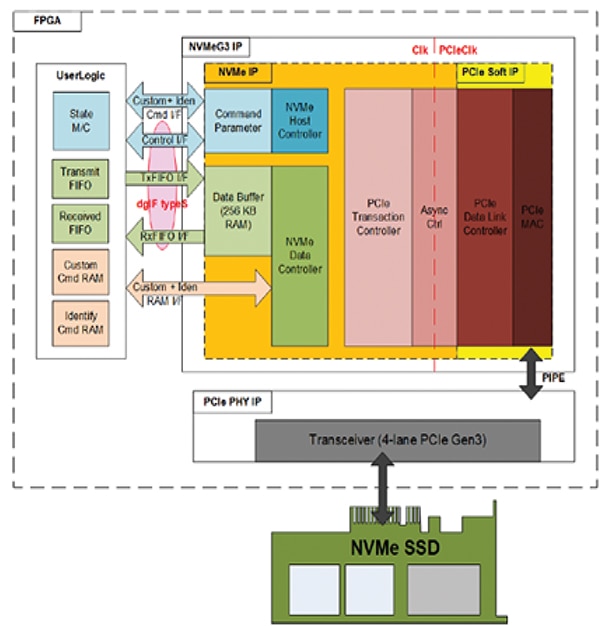

Figura 3: Diagramma a blocchi di NVMeG3-IP. (Immagine per gentile concessione di Design Gateway)

Figura 3: Diagramma a blocchi di NVMeG3-IP. (Immagine per gentile concessione di Design Gateway)

Caratteristiche di NVMeG3-IP

NVMeG3-IP ha molte caratteristiche, alcune delle quali sono illustrate di seguito:

- Permette di implementare il livello dell'applicazione, delle transazioni, dei collegamenti dati e alcune parti dello strato fisico per accedere all'SSD NVMe senza usare la CPU

- Permette di operare con PCIe PHY IP di Xilinx configurato come PCIe Gen3 a 4 canali (interfaccia bus a 128 bit)

- Include un buffer di dati RAM di 256 kB

- Interfaccia utente semplice tramite dgIF typeS

- Supporta sei comandi: Identify, Shutdown, Write, Read, SMART e Flush (più un comando aggiuntivo opzionale)

- Dispositivi NVMe supportati:

- Base Class Code:01h (memoria di massa), Sub Class Code:08h (Non volatile), Interfaccia di programmazione:02h (NVMHCI)

- MPSMIN (dimensione minima pagina di memoria): 0 (4 kB)

- MDTS (dimensione massima di trasferimento dati): almeno 5 (128 kB) o 0 (nessuna limitazione)

- Unità LBA: 512 byte o 4096 byte

- La frequenza di clock dell'utente deve essere maggiore o uguale al clock PCIe (250 MHz per Gen3)

- Progetti di riferimento disponibili:

- ZCU102 con scheda di espansione AB17-M2FMC

- KCU105 con scheda di espansione AB18-PCIeX16/AB16-PCIeXOVR

- VCU118 con scheda di espansione AB18-PCIeX16

Design Gateway ha sviluppato NVMeG3-IP come controller host NVMe per l'accesso a un SSD NVMe. L'interfaccia utente e le caratteristiche standard sono studiate per semplificare l'uso senza dover conoscere il protocollo NVMe. NVMeG3-IP ha inoltre PCIe Soft IP integrato che implementa il livello Data link e alcune parti dello strato fisico del protocollo PCIe con logica pura. NVMeG3-IP può così funzionare in un FPGA, che non ha un blocco integrato PCIe, utilizzando PCIe Soft IP integrato e il core PCIe PHY IP di Xilinx. PCIe PHY IP di Xilinx è un core IP libero che include un transceiver e un equalizzatore logico.

NVMeG3-IP supporta sei comandi NVMe: Identify, Shutdown, Write, Write, Read, SMART e Flush. La BlockRAM da 256 kB è integrata in NVMeG3-IP per fungere da buffer dei dati. Il sistema non ha bisogno di CPU e di memoria esterna. Maggiori informazioni su NVMeG3-IP sono disponibili nella scheda tecnica che può essere scaricata dal nostro sito Web.

Gli usi delle risorse FPGA sul dispositivo FPGA XCZU9EG-2FFVB1156E sono mostrati nella Tabella 1 qui sotto.

|

Tabella 1: Statistiche di un'implementazione di esempio per il dispositivo Ultrascale/Ultrascale+

Implementazione e risultato delle prestazioni su ZCU102

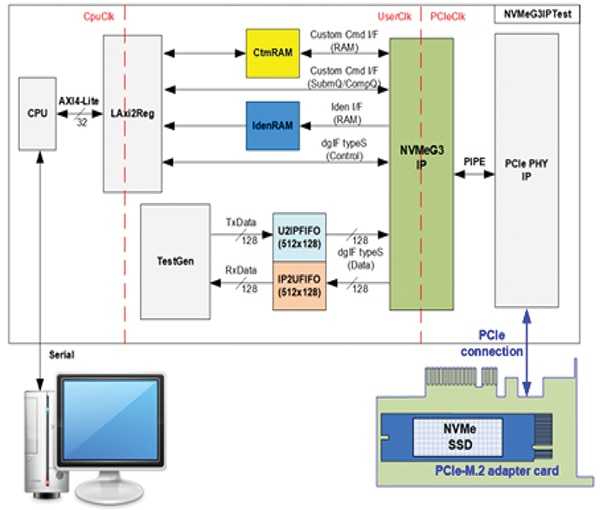

La Figura 4 mostra la panoramica del progetto di riferimento basato su ZCU102 per dimostrare il funzionamento di NVMeG3-IP. Il modulo NVMeG3IPTest del sistema dimostrativo comprende i seguenti moduli: TestGen, LAxi2Reg, CtmRAM, IdenRAM e FIFO.

Per maggiori dettagli sul progetto di riferimento NVMeG3-IP consultare il documento del progetto di riferimento NVMeG3-IP messo a disposizione sul sito Web di Design Gateway.

Figura 4: Panoramica del progetto di riferimento NVMeG3-IP. (Immagine per gentile concessione di Design Gateway)

Figura 4: Panoramica del progetto di riferimento NVMeG3-IP. (Immagine per gentile concessione di Design Gateway)

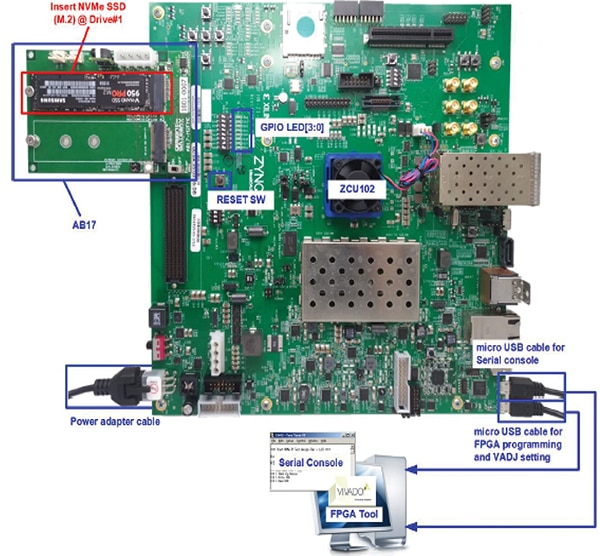

Il sistema di dimostrazione è progettato per scrivere/verificare i dati con SSD NVMe su ZCU102. L'utente controlla il funzionamento del test tramite una console seriale. Per l'interfacciamento di SSD NVMe con ZCU102, occorre una scheda di espansione AB17-M2FMC come mostrato nella Figura 5.

Figura 5: Ambiente dimostrativo di NVMeG3-IP impostato su ZCU102. (Immagine per gentile concessione di Design Gateway)

Figura 5: Ambiente dimostrativo di NVMeG3-IP impostato su ZCU102. (Immagine per gentile concessione di Design Gateway)

Il risultato del test di esempio quando si esegue il sistema dimostrativo su ZCU102 con Samsung 970 Pro da 512 GB è riportato nella Figura 6.

Figura 6: Prestazioni di lettura/scrittura di SSD NVMe su ZCU102 utilizzando Samsung 970 PRO S. (Immagine per gentile concessione di Design Gateway)

Figura 6: Prestazioni di lettura/scrittura di SSD NVMe su ZCU102 utilizzando Samsung 970 PRO S. (Immagine per gentile concessione di Design Gateway)

Conclusione

NVMeG3-IP Core fornisce una soluzione sia per abilitare l'interfaccia SSD NVMe sul kit di valutazione ZCU102 sia per la famiglia di dispositivi MPSoC Zynq® UltraScale+™ di Xilinx® che non hanno un blocco integrato PCIe. NVMeG3-IP è stato progettato per raggiungere le massime prestazioni con il minor utilizzo possibile di risorse FPGA per l'accesso a SSD NVMe senza che sia necessaria una CPU. È particolarmente idoneo per unità di memorizzazione NVMe ad alte prestazioni senza CPU ed è in grado di implementare più interfacce SSD NVMe utilizzando transceiver GTH senza limitazioni derivanti dal numero di blocchi integrati PCIe disponibili sul dispositivo FPGA.

Esonero della responsabilità: le opinioni, le convinzioni e i punti di vista espressi dai vari autori e/o dai partecipanti al forum su questo sito Web non riflettono necessariamente le opinioni, le convinzioni e i punti di vista di DigiKey o le sue politiche.