Creare rapidamente clock a basso jitter e ad alta frequenza con un modulo con anello di traslazione

Contributo di Editori nordamericani di DigiKey

2021-08-04

I progettisti di sistemi di strumentazione e misurazione richiedono segnali a basso jitter e privi di rumore spurio per fornire rapporti segnale/rumore (SNR) o grandezze vettoriali di errore (EVM) necessari per soddisfare le richieste sempre più esigenti dei clienti. Allo stesso tempo, stanno anche affrontando una pressione significativa per ridurre l'ingombro della scheda, così come i costi di progettazione e la complessità. Quest'ultimo è importante per accorciare i tempi di sviluppo e soddisfare i tempi di commercializzazione sempre più veloci.

Per affrontare le numerose sfide, gli ingegneri hanno bisogno di abbandonare le loro soluzioni di clocking di strumentazione e misurazione tradizionalmente discrete e fatte su misura a favore di soluzioni più integrate. Un passo importante in questo senso è l'uso di un PLL (circuito ad aggancio di fase) traslazionale integrato. Questo permette la conversione di frequenza di un segnale tradizionale dell'oscillatore controllato in tensione (VCO), pur mantenendo sostanzialmente il jitter e il rumore di fase di un oscillatore locale esterno fisso (LO).

Questo articolo discute il ruolo dei cicli di traslazione per ottenere il rumore di fase integrato più basso del settore. A titolo di esempio, presenta il SiP (System-in-Package) ADF4401A con anello di traslazione di Analog Devices e mostra come affronta i requisiti di prestazione attraverso un segnale di uscita con capacità di jitter integrato a banda larga sotto i 10 femtosecondi rms e isolamento migliorato per attenuare le componenti spurie, soddisfacendo al contempo le esigenze di integrazione, costo, complessità e time-to-market dei progettisti.

Operazioni PLL tradizionali e anello di traslazione

Lo scopo principale di un anello di traslazione è quello di generare un segnale di uscita bloccato su un segnale di riferimento in ingresso con un rumore di fase in banda significativamente ridotto rispetto ai PLL tradizionali.

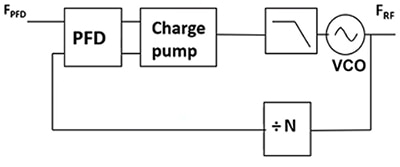

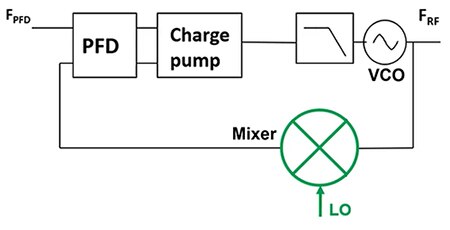

Un PLL standard consiste in un sistema di retroazione contenente un rilevatore a frequenza di fase (PFD), una pompa di carica, un filtro passa-basso (LPF), un VCO e un divisore di frequenza di retroazione N (Figura 1).

Figura 1: Il PLL standard si blocca su un riferimento di frequenza inferiore (FPFD) e genera una frequenza di uscita (FRF) (Immagine per gentile concessione di Bonnie Baker)

Figura 1: Il PLL standard si blocca su un riferimento di frequenza inferiore (FPFD) e genera una frequenza di uscita (FRF) (Immagine per gentile concessione di Bonnie Baker)

Il PFD confronta la fase del riferimento in ingresso e la fase del segnale di retroazione e genera una serie di impulsi proporzionali all'errore di fase. La pompa di carica riceve gli impulsi PFD e li converte in impulsi di source o drain di corrente che a loro volta accordano il VCO in frequenza. L'LPF rimuove tutta l'energia ad alta frequenza degli impulsi e li converte in una tensione che il VCO può utilizzare. Il segnale di uscita del VCO viene riportato al blocco PFD attraverso il divisore N per completare il ciclo.

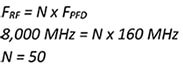

La funzione di trasferimento della frequenza della Figura 1 è calcolata utilizzando l'equazione 1:

![]() Equazione 1

Equazione 1

Dove FRF è la frequenza di uscita

N è il rapporto del divisore di retroazione (può essere intero o frazionario)

FPFD è la frequenza PFD

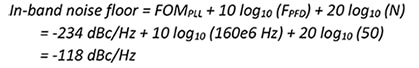

Il rumore di fondo in banda della Figura 1 è calcolato usando l'equazione 2:

![]() Equazione 2

Equazione 2

Dove FOMPLL è la cifra di merito (FOM) del rumore di fondo di fase in banda del PLL

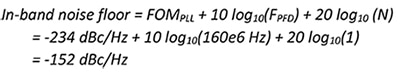

Consideriamo un esempio con un FOM del rumore di fondo di fase in banda di -234 dB/Hz, una frequenza PFD (FPFD) di 160 MHz e una frequenza di uscita (FRF) di 8 GHz.

Per questo sistema, l'equazione 1 è usata per calcolare il valore di N:

L'equazione 2 è usata per calcolare il rumore di fondo in banda:

Nel calcolo di cui sopra, il divisore N contribuisce fortemente al rumore di fondo complessivo in banda, con 20 log10 (50), pari a 34 dB. Un valore N più piccolo diminuirebbe il rumore di fondo in banda; tuttavia, diminuirebbe anche la frequenza di uscita. Quindi, come possiamo generare un'alta frequenza di uscita e mantenere un guadagno dell'anello più basso (N)?

Figura 2: Per un PLL standard in questo esempio, il rumore dal divisore di retroazione (20 log10(N)) ha un rumore in banda superiore di 34 dB rispetto al grafico giallo inferiore dove N = 1 (Immagine per gentile concessione di Bonnie Baker)

Figura 2: Per un PLL standard in questo esempio, il rumore dal divisore di retroazione (20 log10(N)) ha un rumore in banda superiore di 34 dB rispetto al grafico giallo inferiore dove N = 1 (Immagine per gentile concessione di Bonnie Baker)

La soluzione a questo problema è sostituire il divisore N con uno stadio di miscelazione con conversione a scalare (Figura 3).

Figura 3: Un anello di traslazione usa un miscelatore per convertire la frequenza VCO alla frequenza PFD invece di usare un divisore di retroazione tradizionale. (Immagine per gentile concessione di Bonnie Baker)

Figura 3: Un anello di traslazione usa un miscelatore per convertire la frequenza VCO alla frequenza PFD invece di usare un divisore di retroazione tradizionale. (Immagine per gentile concessione di Bonnie Baker)

Nella Figura 3, il miscelatore sostituisce il divisore di retroazione N, risultando in un guadagno dell'anello uguale a 1 (N=1). Questa operazione diminuirà notevolmente il contributo dell'anello di retroazione al rumore di fondo in banda. Per il calcolo del rumore in banda, il valore di N è ora uguale a 1. Usando l'equazione 2, il rumore di fondo in banda per il sistema modificato è il seguente:

Il nuovo rumore in banda mostra un miglioramento di 34 dBc/Hz.

Nella Figura 3, il miscelatore dipende da un LO a bassissimo rumore, chiamato LO di offset. FLO ± FRF deve essere uguale a FPFD per ottenere il blocco.

Con l'architettura dell'anello di traslazione, il rumore di fase del LO di offset è molto importante per ottenere le migliori prestazioni all'uscita RF. Per questo motivo, gli ingegneri in genere progettano un LO di offset basato su onde acustiche di superficie (SAW) controllate in tensione o oscillatori (VCSO) o generatori a pettine o oscillatori con risonatore dielettrico (DRO). NOTA: per il supporto alla progettazione di un LO di offset, contattare Analog Devices.

Sfide dell'anello di traslazione

Tradizionalmente, la progettazione di un anello di traslazione a basso rumore comporta l'implementazione di numerosi blocchi circuitali, che risultano in un progetto complesso, grande e dalla flessibilità limitata. Inoltre, l'intero circuito deve essere convalidato e caratterizzato per il funzionamento finale. Ad esempio, una delle principali preoccupazioni è la perdita di LO (isolamento da LO a RF) al segnale di uscita RF. Questo è un problema significativo per gli ingegneri. Con i progetti tradizionali, gli ingegneri di solito procedono tra più iterazioni per ottenere prestazioni ottimizzate e un isolamento adeguato.

La Figura 3 mostra come ADF4401A integra i principali blocchi circuitali per fornire una soluzione completamente caratterizzata ed elimina le aree tradizionalmente difficili relative alle prestazioni e all'isolamento nei progetti di anello di traslazione. Questa soluzione programmabile permette agli ingegneri di ottenere prestazioni ottimizzate al primo sforzo e di abbattere il time-to-market.

Valutazione di ADF4401A

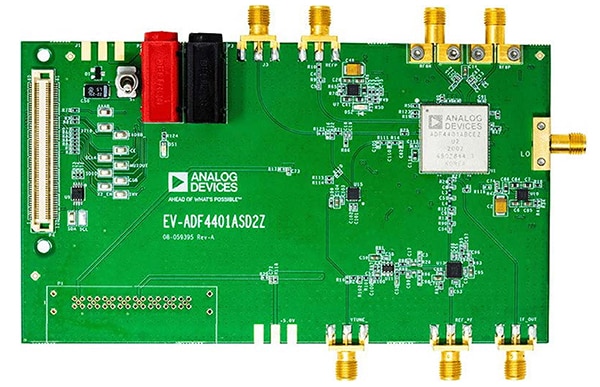

ADF4401A è progettato per aiutare gli ingegneri a abbattere il time-to-market della strumentazione ad alte prestazioni, utilizzando una soluzione di generazione di frequenza con una larghezza di banda RF da 62,5 MHz a 8 GHz. Utilizzando un miscelatore con conversione a scalare, ADF4401A ha un rumore in banda molto basso con un jitter a banda larga di ~9 fs integrato da 100 Hz a 100 MHz. Le tecniche di progettazione e di layout in ADF4401A permettono una gamma dinamica tipica senza spurie di 90 dBc. Un contenitore di 18 x 18 x 2,018 mm riduce sensibilmente lo spazio sulla scheda rispetto a un progetto discreto tradizionale.

Per valutare le prestazioni del dispositivo, i progettisti possono utilizzare la scheda di valutazione EV-ADF4401ASD2Z (Figura 4). Questa scheda include un anello di traslazione completo, compreso un PFD esterno (HMC3716), un filtro attivo (LT6200) e un multiplatore (ADG1609).

Figura 4: La scheda di valutazione EV-ADF4401ASD2Z per il modulo con anello di traslazione ADF4401A include un PFD esterno, un'interfaccia USB e regolatori di tensione (Immagine per gentile concessione di Analog Devices)

Figura 4: La scheda di valutazione EV-ADF4401ASD2Z per il modulo con anello di traslazione ADF4401A include un PFD esterno, un'interfaccia USB e regolatori di tensione (Immagine per gentile concessione di Analog Devices)

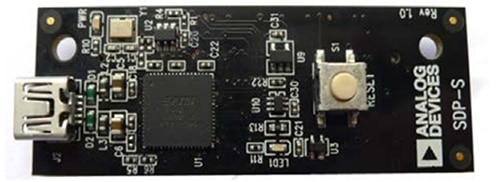

EV-ADF4401ASD2Z include il SiP TL ADF4401A con VCO integrato, un filtro ad anello (5 MHz), un PFD, un'interfaccia USB e regolatori di tensione. Inoltre, EV-ADF4401ASD2Z richiede la scheda di controllo (seriale) EVAL-SDP-CS1Z (SDP-S) come piattaforma dimostrativa di sistema (SDP) (Figura 5). La scheda fornisce una connessione USB da un PC a EV-ADF4401ASD2Z che ne permette la programmazione. La scheda del controller non è fornita nel kit EV-ADF4401ASD2Z.

Figura 5: La scheda di controllo EVAL-SDP-CS1Z (o SDP-S) è necessaria per fornire una connessione USB a EV-ADF4401ASD2Z a un PC per la programmazione (Immagine per gentile concessione di Analog Devices)

Figura 5: La scheda di controllo EVAL-SDP-CS1Z (o SDP-S) è necessaria per fornire una connessione USB a EV-ADF4401ASD2Z a un PC per la programmazione (Immagine per gentile concessione di Analog Devices)

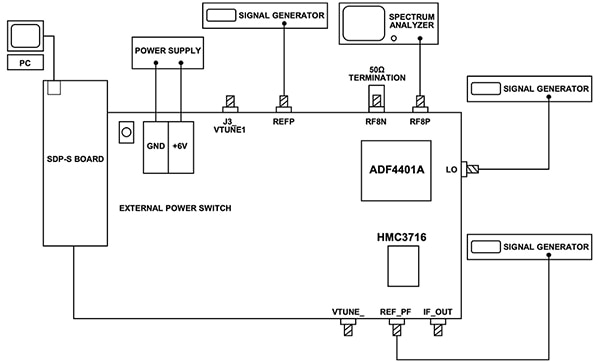

La Figura 6 mostra le connessioni fisiche del sistema EV-ADF4401ASD2Z. Il software associato Analysis | Control | Evaluation (ACE) controlla le funzioni del SiP TL. L'alimentazione proviene da un alimentatore a 6 V applicato esternamente.

Figura 6: Schema dell'impostazione di EV-ADF4401ASD2Z che mostra l'attrezzatura e le connessioni necessarie per valutare ADF4401A, inclusi la scheda di controllo SDP-S, il PC, l'alimentazione, i generatori di segnale e l'analizzatore di spettro (Immagine per gentile concessione di Analog Devices)

Figura 6: Schema dell'impostazione di EV-ADF4401ASD2Z che mostra l'attrezzatura e le connessioni necessarie per valutare ADF4401A, inclusi la scheda di controllo SDP-S, il PC, l'alimentazione, i generatori di segnale e l'analizzatore di spettro (Immagine per gentile concessione di Analog Devices)

L'attrezzatura suggerita da usare con questa scheda di valutazione include un PC Windows, un analizzatore di spettro o un analizzatore di fonti di segnale e tre generatori di segnali.

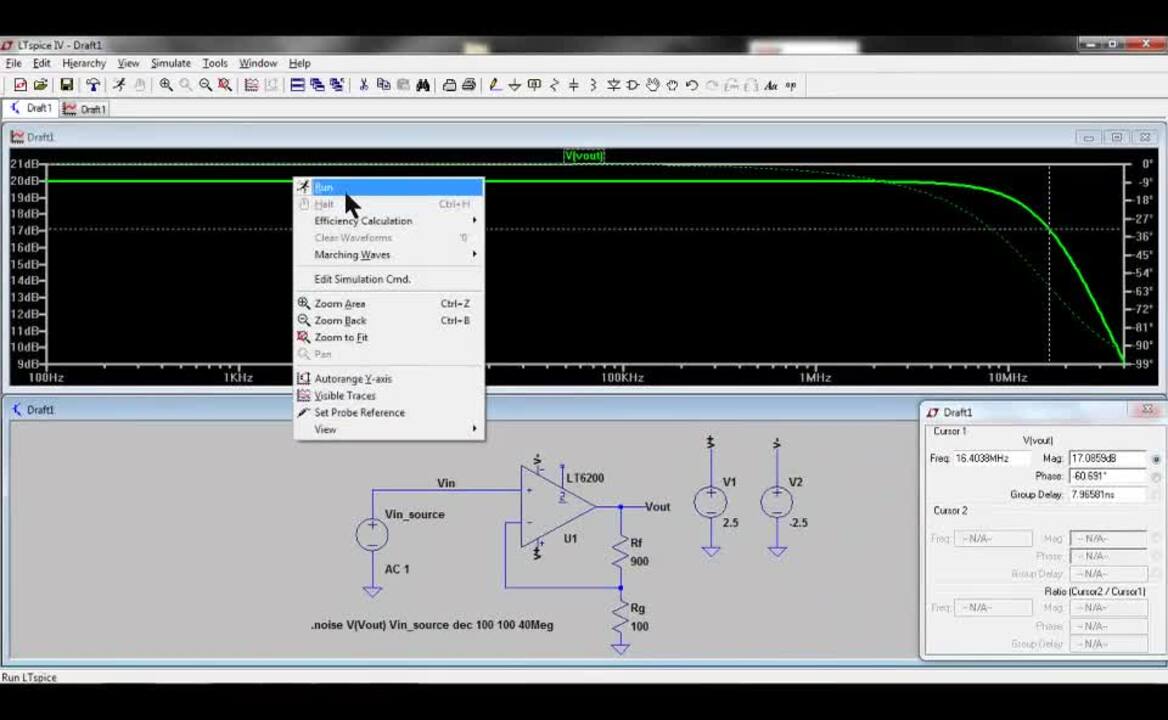

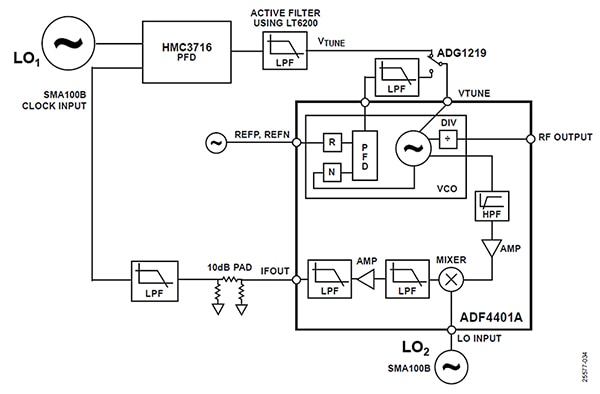

Il diagramma a blocchi EV-ADF4401ASD2Z mostra il modulo ADF4401A, insieme al PFD HMC3716 di Analog Devices, l'amplificatore operazionale LT6200 e l'interruttore SPDT ADG1219 (Figura 7).

Figura 7: Il diagramma a blocchi della scheda di valutazione EV-ADF4401ASD2Z mostra i componenti chiave che supportano l'anello di traslazione AD4401A (Immagine per gentile concessione di Analog Devices)

Figura 7: Il diagramma a blocchi della scheda di valutazione EV-ADF4401ASD2Z mostra i componenti chiave che supportano l'anello di traslazione AD4401A (Immagine per gentile concessione di Analog Devices)

È fondamentale usare un PFD che possa operare alle alte frequenze, perché questo riduce la necessità di ricorrere a divisori che possono degradare la risposta al rumore in banda. La capacità di frequenza di confronto di fase a 1,3 GHz di HMC3716 di Analog Devices lo rende ideale per l'uso nel campo IF di ADF4401A. La capacità di un tale circuito di confrontare sia la frequenza che la fase elimina la necessità di un circuito aggiuntivo per indirizzare la frequenza verso la frequenza di uscita prevista. HMC3716 diventa il PFD esterno per completare l'anello di offset. L'intervallo di funzionamento ad alta frequenza e il rumore di fase ultra-basso di HMC3716 permettono di progettare filtri ad anello ad ampia larghezza di banda.

Nella Figura 7, l'amplificatore operazionale LT6200 con una configurazione LPF attenua i segnali spuri ad alta frequenza, mentre l'interruttore ADG1219 completa l'anello di traslazione del sistema.

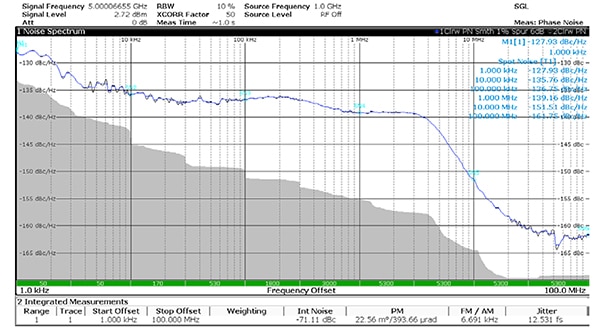

L'apparecchio di valutazione EV-ADF4401ASD2Z crea grafici del rumore in banda e misurazioni del jitter come mostra la Figura 8.

Figura 8: Rumore di fase a banda laterale singola in uscita a 5 GHz, con un riferimento esterno HMC3716 di 500 MHz e LO esterno a 4,5 GHz (Immagine per gentile concessione di Analog Devices)

Figura 8: Rumore di fase a banda laterale singola in uscita a 5 GHz, con un riferimento esterno HMC3716 di 500 MHz e LO esterno a 4,5 GHz (Immagine per gentile concessione di Analog Devices)

Nella Figura 8, l'ingresso LO2 e HMC3716 è un generatore di segnali RF e microonde SMA100B. Il rumore in banda LO2 della scheda di valutazione è di circa -135 dBc/Hz che appare evidente a bassi offset fino a 300 kHz. LO2, il modulo ADF4401A, il PFD HMC3716 e il filtro ad anello contribuiscono a un rumore in banda di circa -140 dBc/Hz. Il rumore di fase interno appare tra 5 MHz e 50 MHz e il rumore di fase di fondo dell'apparecchio è di circa -160 dBc/Hz. Insieme, generano un jitter rms di 12,53 fs in totale.

Conclusione

I sistemi di strumentazione ad alta velocità richiedono clock a bassissimo jitter per garantire che i dati in uscita non siano compromessi. La sfida per gli ingegneri è quella di trovare dispositivi adatti per un sistema di clock a gigahertz ad alta velocità. L'anello di traslazione ADF4401A semplifica notevolmente la selezione del dispositivo per creare il sistema di clock, fornendo un modulo compatto che assicura un basso jitter alle frequenze più alte, riducendo anche lo spazio su scheda, i costi e il time-to-market.

Esonero della responsabilità: le opinioni, le convinzioni e i punti di vista espressi dai vari autori e/o dai partecipanti al forum su questo sito Web non riflettono necessariamente le opinioni, le convinzioni e i punti di vista di DigiKey o le sue politiche.