Utilizzare un processore multicore per realizzare prodotti intelligenti multimediali a basso consumo

Contributo di Editori nordamericani di DigiKey

2019-03-26

I prodotti intelligenti, oltre ai tradizionali requisiti dei progetti embedded in tempo reale, richiedono sempre più un software applicativo più esigente. A parte un maggiore carico di calcolo, questi prodotti devono supportare l'interazione dell'utente con servizi multimediali avanzati come touchscreen, grafica 3D ad alta risoluzione e sensori di immagini.

Gli sviluppatori devono pertanto far fronte all'incremento sia dei requisiti tecnici che della domanda di ridurre costi e dimensioni del sistema e sono costretti a trovare un'alternativa più efficace ai tradizionali progetti basati su sottosistemi multipli.

Questo articolo tratterà dell'evoluzione dei requisiti di progettazione e di come i processori li hanno finora soddisfatti. Quindi presenterà e mostrerà come utilizzare i nuovi processori di NXP Semiconductors. Questi processori offrono agli sviluppatori una soluzione più semplice per rispondere alla crescente domanda di progetti in grado di gestire sia i requisiti di elaborazione in tempo reale che quelli di calcolo dell'applicazione.

Scalare i processori per preservare l'investimento nel codice

Era consuetudine che gli sviluppatori scalassero la potenza di calcolo dei progetti usando microprocessori costruiti con core supplementari abbinati a specifici requisiti di elaborazione delle applicazioni. Questo metodo permetteva loro di ottenere un incremento delle prestazioni mantenendo la compatibilità con il codice base esistente e l'esperienza con quella famiglia di dispositivi.

Con la serie di processori per applicazioni i.MX 6 di NXP, ad esempio, potevano mantenere la compatibilità del codice anche se scalavano le prestazioni utilizzando un microprocessore i.MX 6Solo con un unico processore per applicazioni Arm® Cortex®-A9, un i.MX 6Dual dual core o un i.MX 6Quad quad core.

La stessa esigenza di scalabilità di elaborazione delle applicazioni si sta evolvendo rapidamente in progetti che un tempo erano considerati sistemi embedded tradizionali. Grazie a questi progetti, i costruttori cercano di aggiungere intelligenza anche agli elettrodomestici, ai controller industriali e agli strumenti medicali. I fornitori di semiconduttori hanno risposto con dispositivi di elaborazione multicore eterogenea (HMP) che integrano sia core del processore per applicazioni che core del processore embedded. Ad esempio, la famiglia i.MX 8M di NXP combina fino a quattro core del processore per applicazioni Arm Cortex-A53 con un core del processore embedded Arm Cortex-M4.

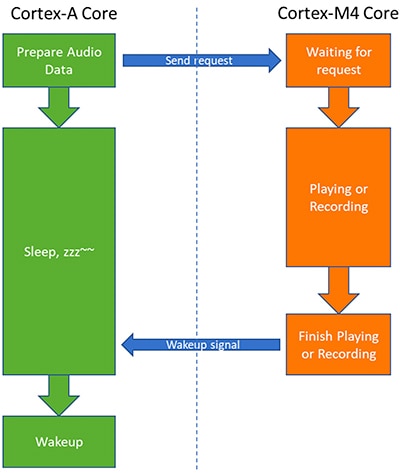

Con quest'unico dispositivo, gli sviluppatori possono creare prodotti audio intelligenti che sfruttano pienamente il processore per migliorare, filtrare o manipolare in altro modo i dati audio. Il sistema audio si affida quindi al core del processore embedded per eseguire le funzioni in tempo reale necessarie per la riproduzione (Figura 1). Mentre le operazioni in tempo reale vengono svolte nel processore embedded, per ridurre il consumo energetico complessivo il processore per applicazioni può essere messo in modalità basso consumo. Al termine delle operazioni in tempo reale, il processore embedded invia semplicemente un segnale di riattivazione al processore per applicazioni.

Figura 1: I processori multicore eterogenei sono particolarmente efficaci per la progettazione di prodotti intelligenti, assicurando funzionalità di calcolo sia ad alte prestazioni che in tempo reale senza compromettere i budget energetici ristretti. (Immagine per gentile concessione di NXP Semiconductors)

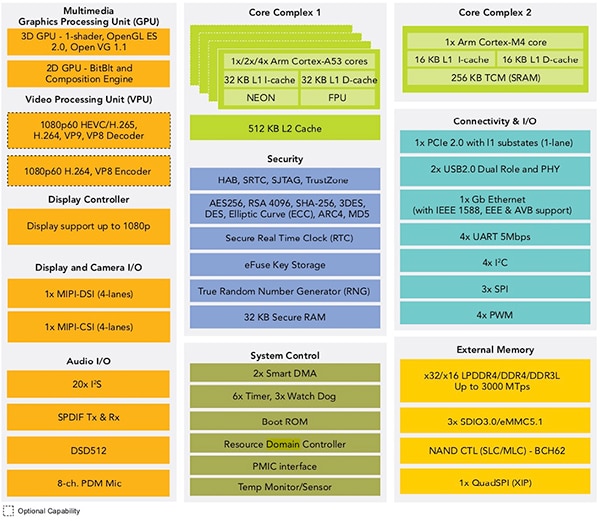

Assieme ai core eterogenei, la famiglia i.MX 8M di NXP integra un ampio set di risorse multimediali tra cui un'unità di elaborazione video 4K (VPU) e un'unità di elaborazione grafica (GPU) 3D ad alte prestazioni. Di conseguenza, può fornire una soluzione efficace per una crescente classe di prodotti video e di grafica 3D intelligenti.

Ciononostante, gli sviluppatori che costruiscono sistemi ad alte prestazioni devono far fronte alla crescente domanda di minori consumi energetici sia per i sistemi a batteria che per quelli alimentati dalla linea. Per venire a capo del problema, la famiglia di processori i.MX 8M Mini di NXP è realizzata con un'avanzata tecnologia di processo dei semiconduttori che risolve i conflitti dei requisiti di elaborazione di carico misto ad alte prestazioni e di riduzione del consumo energetico.

Calcolo ad alte prestazioni e basso consumo

Essendo la prima famiglia HMP di NXP realizzata con una tecnologia di processo FinFET da 14 nm, i suoi processori i.MX 8M Mini sono progettati per i sistemi emergenti di Internet delle cose (IoT) e IIoT che combinano requisiti di alte prestazioni, sicurezza robusta e basso consumo. Come nel caso della famiglia i.MX 8M di NXP, i.MX 8M Mini integra un Arm Cortex-M4 per l'elaborazione embedded con un massimo di quattro core Arm Cortex-A53 per l'elaborazione delle applicazioni, insieme a un sottosistema completo di sicurezza e a molteplici opzioni di connettività e I/O (Figura 2).

Figura 2: Il processore i.MX 8M Mini di NXP combina fino a quattro core del processore per applicazioni Arm Cortex-A53 con un core embedded Arm Cortex-M4 ed è corredato di un set completo di funzioni di sistema di sicurezza, multimediali e di interfacce I/O richieste nei prodotti intelligenti emergenti. (Immagine per gentile concessione di NXP Semiconductors)

Per assolvere al proprio ruolo nei progetti embedded, i.MX 8M Mini riduce il numero di alcuni canali I/O e le capacità ad alta risoluzione del suo sottosistema multimediale rispetto al precedente i.MX 8M di NXP. Ad esempio, i dispositivi i.MX 8M Mini, comprese le versioni commerciali (MIMX8MM6DVTLZAA) e industriali (MIMX8MM6CVTKZAAA), offrono una GPU shader e una VPU 1080p a 60 Hz rispetto alle quattro GPU shader e alla VPU 4K di i.MX 8M di NXP. Altri membri della famiglia i.MX 8M Mini, compresi i dispositivi commerciali (MIMX8MM5DVTLZAA) e industriali (MIMX8MM5CVTKZAA), eliminano completamente la VPU. Come con il precedente i.MX 8M di NXP, i.MX 8M Mini consente agli sviluppatori di bilanciare ulteriormente prestazioni e costi sfruttando il supporto del processore per diversi tipi di memoria, compresa tensione DDR3L (doppia velocità 3 bassa tensione), DDR4 e LPDDR4 (DDR4 a bassa potenza).

Consumo energetico ridotto

Per migliorare ulteriormente le prestazioni e il consumo energetico, gli sviluppatori possono sfruttare la capacità di i.MX 8M Mini di NXP di passare automaticamente o tramite codice a modalità operative che consumano meno energia. In determinate condizioni, i core dell'applicazione possono passare automaticamente alla modalità inattiva, disattivando GPU, VPU e core dell'applicazione, effettuando contemporaneamente il clock gating della maggior parte della logica interna senza interrompere l'alimentazione alla cache dei dati L2. In questa modalità, il core Arm Cortex-M4 può anche continuare a funzionare per eseguire attività di elaborazione embedded più tradizionali come l'acquisizione dei dati del sensore.

La modalità di sospensione è quella più efficiente dal punto di vista energetico, estendendo la riduzione dei consumi applicata in stato di inattività disattivando anche il DDRC (controller a doppia velocità dati) che gestisce le interfacce di memoria. Infine, la modalità di storage di dati non volatile sicura (SNVS) mantiene l'alimentazione solo alla logica SNVS e al clock in tempo reale.

Le caratteristiche di riduzione dei consumi della tecnologia di processo FinFET a 14 nm utilizzata in i.MX 8M risultano particolarmente evidenti nelle modalità di sospensione e SNVS. In i.MX 8M Mini con FinFET, la modalità di sospensione consuma circa 7,81 mW. Nel precedente i.MX 8M, la modalità simile dal punto di vista funzionale (chiamata modalità di sospensione profonda) consuma 197 mW. Una riduzione analoga si applica nella modalità SNVS, dove i.MX 8M Mini consuma circa 0,11 mW, mentre il precedente i.MX 8M consuma circa 17 mW.

Visti tutti i blocchi funzionali e le modalità operative ottimizzate in dispositivi complessi come i.MX 8M Mini, gli ingegneri devono far fronte a numerosi requisiti rigorosi di implementazione. Come accade con altri dispositivi di questa classe, per ottimizzare la gestione e l'efficienza energetica i.MX 8M Mini si affida a più domini di potenza. Per avviare e arrestare questi dispositivi occorre rispettare scrupolosamente le sequenze specificate per l'accensione e lo spegnimento.

All'accensione, per prima cosa i.MX 8M Mini applica energia, in genere 1,8 V, al pre-driver GPIO nel banco SNVS. Entro 2 ms (massimo 2,4 ms), occorre applicare 0,8 V (tipico) alla logica core SNVS. Questo processo continua con segnali specifici o con l'applicazione in sequenza di energia ai pin di i.MX 8M Mini attraverso altre 12 fasi, ognuna delle quali è temporizzata per avvenire entro intervalli compresi tra 0,015 ms e 20 ms.

Per spegnere il dispositivo viene applicata la sequenza inversa, ma con un ritardo uniforme di 10 ms tra gli stadi sequenziali. In entrambi i casi, il mancato rispetto di queste linee guida può impedire l'avvio del dispositivo, causare una corrente eccessiva durante l'accensione o, nel caso peggiore, provocare danni irreversibili al dispositivo.

La progettazione fisica di una scheda CS per il processore ha rigidi requisiti propri. Per la configurazione del contenitore del processore di 14x14 mm con 486 sfere, per rimanere all'interno delle linee guida sulla caduta della corrente-resistenza (IR) NXP consiglia di utilizzare una scheda CS con un numero di strati sufficienti - almeno otto - dedicati ai rail di alimentazione. Allo stesso tempo, gli ingegneri del layout devono garantire una diafonia minima sulle linee ad alta velocità, comprese quelle per i dispositivi di memoria supportati che operano a velocità di 1,5 GHz e di 3000 MT/s.

Sviluppo rapido

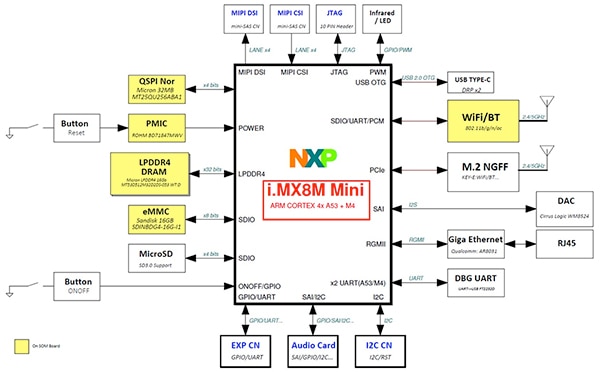

Per aiutare gli ingegneri ad accelerare lo sviluppo di applicazioni o di progetti hardware personalizzati, NXP fornisce il kit di valutazione i.MX 8M Mini EVK e il relativo progetto di riferimento (Figura 3). Fornito come scheda base e scheda SoM, il kit di valutazione offre un sistema completo che comprende memoria LPDDR4 esterna e flash, nonché USB e altre interfacce.

Figura 3: Il set di schede i.MX 8M Mini EVK di NXP offre una piattaforma di sistema completa per poter valutare immediatamente i processori i.MX 8M Mini e sviluppare rapidamente applicazioni a processori multicore eterogenei. (Immagine per gentile concessione di NXP Semiconductors)

Oltre a Gigabit Ethernet, per le opzioni di connettività il kit include Wi-Fi e Bluetooth. Schede aggiuntive, compresi il modulo videocamera MINISASTOCSI e il touchscreen OLED (diodo organico a emissione di luce) MX8-DSI-OLED1, completano il progetto di applicazioni video e display.

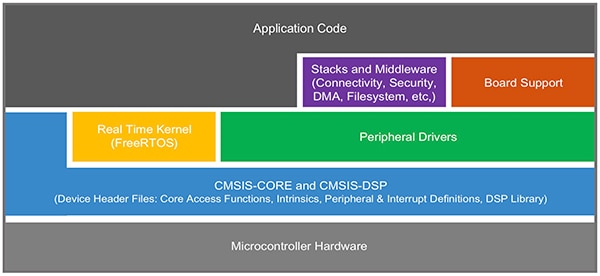

Grazie alle immagini precostruite per gli ambienti operativi Embedded Linux® ed Embedded Android®, gli sviluppatori possono usare immediatamente il kit per valutare il processore i.MX 8M Mini ed eseguire applicazioni di esempio. Agli sviluppatori che desiderano realizzare applicazioni software proprie, NXP offre il kit di sviluppo software (SDK) gratuito MCUXpresso che mette a disposizione un set completo di componenti software per costruire una tipica applicazione embedded ad alte prestazioni (Figura 4).

Figura 4: L'architettura del kit di sviluppo software (SDK) MCUXpresso comprende l'intero set di strati software, inclusi driver, contenitore di supporto scheda e i componenti opzionali richiesti per lo sviluppo della maggior parte delle applicazioni embedded. (Immagine per gentile concessione di NXP Semiconductors)

Utilizzando il dashboard MCUXpresso SDK online di NXP, gli sviluppatori possono definire una configurazione SDK per la toolchain GCC Arm Embedded o IAR Embedded Workbench per Arm. Il dashboard consente inoltre di aggiungere altri componenti middleware opzionali, compresi la libreria DSP Arm Cortex Microcontroller Software Interface Standard (CMSIS) e Amazon FreeRTOS. La distribuzione SDK configurata viene offerta completa delle librerie Arm standard, dei driver di periferica e dei driver wrapper di periferica per FreeRTOS, oltre a una serie molto nutrita di esempi di software. Tra gli esempi di software nella distribuzione SDK, un paio di applicazioni dimostra un modello di progettazione di scambio di messaggi chiave fondamentale per elaborazioni eterogenee.

In qualsiasi ambiente di calcolo multicore, processori separati richiedono meccanismi efficienti per passare le richieste e condividere i dati. Per le applicazioni i.MX 8M Mini EVK, NXP utilizza RPMsg-Lite, una versione leggera del protocollo Remote Processor Messaging (RPMsg). Il protocollo RPMsg è stato creato nell'ambito del progetto quadro Open Asymmetric Multi Processing (OpenAMP) per fornire un'interfaccia standard per la comunicazione tra più core in un sistema multicore eterogeneo. RPMsg-Lite di NXP affronta il problema delle limitazioni in materia di risorse nei sistemi embedded più piccoli, fornendo un ingombro ridotto ed eliminando funzionalità non coerenti con questi sistemi.

Nell'ambito della distribuzione SDK, un'applicazione di esempio, rpmsg_lite_pingpong_rtos, dimostra uno scambio basilare usando RPMsg-Lite per implementare una semplice interazione ping-pong tra vari processori (Listato 1). Dopo aver creato una coda RPMsg (my_queue) e un endpoint (my_ept) per l'altro processore "remoto", il processore per applicazioni "host" segnala il core remoto. Quando riceve una risposta handshake dal core remoto, l'host inizia un processo ad anello che usa un'attesa in stato di blocco per un messaggio "ping" dal processore remoto prima di inviare la propria risposta "pong".

Copy

void app_task(void *param)

{

.

.

.

my_rpmsg = rpmsg_lite_remote_init((void *)RPMSG_LITE_SHMEM_BASE, RPMSG_LITE_LINK_ID, RL_NO_FLAGS);

while (!rpmsg_lite_is_link_up(my_rpmsg))

;

PRINTF("Link is up!\r\n");

my_queue = rpmsg_queue_create(my_rpmsg);

my_ept = rpmsg_lite_create_ept(my_rpmsg, LOCAL_EPT_ADDR, rpmsg_queue_rx_cb, my_queue);

ns_handle = rpmsg_ns_bind(my_rpmsg, app_nameservice_isr_cb, NULL);

rpmsg_ns_announce(my_rpmsg, my_ept, RPMSG_LITE_NS_ANNOUNCE_STRING, RL_NS_CREATE);

PRINTF("Nameservice announce sent.\r\n");

/* Wait Hello handshake message from Remote Core. */

rpmsg_queue_recv(my_rpmsg, my_queue, (unsigned long *)&remote_addr, helloMsg, sizeof(helloMsg), NULL, RL_BLOCK);

while (msg.DATA <= 100)

{

PRINTF("Waiting for ping...\r\n");

rpmsg_queue_recv(my_rpmsg, my_queue, (unsigned long *)&remote_addr, (char *)&msg, sizeof(THE_MESSAGE), NULL,

RL_BLOCK);

msg.DATA++;

PRINTF("Sending pong...\r\n");

rpmsg_lite_send(my_rpmsg, my_ept, remote_addr, (char *)&msg, sizeof(THE_MESSAGE), RL_BLOCK);

}

PRINTF("Ping pong done, deinitializing...\r\n");

rpmsg_lite_destroy_ept(my_rpmsg, my_ept);

my_ept = NULL;

rpmsg_queue_destroy(my_rpmsg, my_queue);

my_queue = NULL;

rpmsg_ns_unbind(my_rpmsg, ns_handle);

rpmsg_lite_deinit(my_rpmsg);

msg.DATA = 0;

.

.

.

}

Listato 1: Questo frammento del codice di esempio fornito nel kit di sviluppo software MCUXpresso dimostra il modello di progettazione di base per l'esecuzione di interazioni tra vari processori in un processore multicore eterogeneo. (Codice per gentile concessione di NXP Semiconductors)

Gli sviluppatori possono facilmente partire da questo semplice scambio per creare operazioni complete preposte ad assegnare l'esecuzione delle attività a più processori. Un'altra applicazione di esempio, sai_low_power_audio, usa RPMsg-Lite essenzialmente come strato di collegamento dati di basso livello per un protocollo di applicazioni Simplified Real Time Messaging (SRTM) di livello superiore. In questa applicazione, un processore Arm Cortex-A53 usa questo protocollo SRTM per chiedere al protocollo Arm Cortex-M4 di riprodurre un file audio che si trova nella memoria condivisa. Dopo aver assunto il controllo del buffer condiviso, M4 esegue diverse operazioni fra cui, da ultimo, una transazione SDMA (Smart Direct Memory Access) per trasferire i dati al codice appropriato e infine all'interfaccia audio seriale (SAI) per l'uscita audio. Durante l'operazione, il core A53 può entrare in modalità a bassa potenza. Sebbene abbia una progettazione più complessa di quella dell'applicazione ping-pong, l'applicazione di esempio sai_low_power_audio dimostra come gli sviluppatori possono usare processori multicore eterogenei per massimizzare le prestazioni e, allo stesso tempo, ridurre il consumo energetico dei prodotti intelligenti.

Conclusione

Nei prodotti intelligenti, i tradizionali sistemi di elaborazione embedded in tempo reale si accompagnano a elevate capacità di elaborazione dell'applicazione. Ciononostante, gli sviluppatori devono soddisfare sia questi requisiti di elaborazione che le aspettative di prodotti a minor consumo energetico, tanto in sistemi a batteria che in quelli alimentati dalla linea.

Realizzato con un'avanzata tecnologia dei semiconduttori, il processore per applicazioni i.MX 8M Mini di NXP offre la combinazione richiesta di basso consumo e capacità di elaborazione multicore eterogenee ad alte prestazioni. Grazie ai dispositivi i.MX 8M Mini di NXP, gli sviluppatori possono rispondere in modo più efficiente ai requisiti emergenti di capacità di calcolo ad alte prestazioni in progetti di sistemi embedded, richieste nei sempre più sofisticati prodotti intelligenti.

Esonero della responsabilità: le opinioni, le convinzioni e i punti di vista espressi dai vari autori e/o dai partecipanti al forum su questo sito Web non riflettono necessariamente le opinioni, le convinzioni e i punti di vista di DigiKey o le sue politiche.