Utilizzare microcontroller Flashless per abbassare i costi dei sistemi e migliorare le prestazioni

Contributo di Editori nordamericani di DigiKey

2019-08-22

Le reti di Internet delle cose (IoT) sono chiamate a svolgere compiti sempre più complessi. Questa tendenza ha aumentato i requisiti di memoria degli endpoint IoT, soprattutto di quelli che ora eseguono livelli più elevati di edge computing. Tuttavia, la memoria flash integrata del microcontroller è limitata a circa 1 megabit, largamente insufficiente per molti endpoint IoT di fascia alta.

La soluzione convenzionale era quella di espandere la memoria di programma del microcontroller con un chip flash esterno. Quando però servono 8 Mbit o più, la maggior parte della memoria di programma non rientra più sul chip.

Di conseguenza, in molti casi i progettisti potrebbero essere più propensi a rinunciare completamente alla flash su chip e utilizzare invece un microcontroller Flashless - anche detto ROMless - accoppiato con un chip flash SPI eXecute-in-place (XiP) ottale ad alta velocità esterno. Questa soluzione riduce notevolmente il costo del microcontroller e assicura il successo anche futuro del progetto consentendo una maggiore scalabilità. Tutte le preoccupazioni sui tempi di accesso alla memoria sono superate dalla comparsa di interfacce di memoria ottale ad altissima velocità.

Questo articolo prende in esame i microcontroller ROMless, le memorie esterne e la loro evoluzione in un'opzione valida per gli endpoint IoT e i sistemi embedded che richiedono grandi quantità di memoria di programma. Illustra poi come applicare il concetto tramite i microcontroller ROMless di NXP Semiconductors e un chip flash SPI XiP ottale di Adesto Technologies.

Espansione della memoria sull'edge IoT

La maggior parte degli endpoint IoT con prestazioni medio-basse utilizza un microcontroller per gestire l'endpoint, memorizzando il firmware in una flash su chip. L'aggiunta di ulteriore codice applicativo, stack di comunicazione IP wireless e codice di sicurezza più potente porta alla dilatazione del firmware. Tale incremento dimensionale del codice può avvenire durante lo sviluppo e a seguito di aggiornamenti sul campo.

Ad alcuni di questi endpoint IoT ora si chiedono maggiori funzioni di calcolo. Invece di trasmettere attraverso la rete i dati grezzi o parzialmente elaborati dei sensori a un computer centrale affinché li elabori, questi endpoint IoT svolgono compiti più complessi che possono includere algoritmi di fusione dei sensori, interpolazione dei dati, riconoscimento di modelli o immagini e calcoli basati su intelligenza artificiale (IA) sempre più complessi.

Poiché il computer centrale riceve solo il risultato dell'elaborazione locale del nodo IoT invece di ogni byte dei dati grezzi del sensore, il traffico sulla rete wireless viene ridimensionato. Il trasmettitore RF può essere l'elemento che assorbe più potenza in un endpoint IoT, per cui l'edge computing si traduce spesso in una maggiore durata della batteria per gli endpoint alimentati a batteria.

I sistemi che devono essere aggiornati sul campo si trovano ad affrontare ulteriori sfide di memoria. Per gestire questi aggiornamenti, i sistemi convenzionali richiedono almeno due volte lo spazio di memoria stimato per il programma. Questo spazio serve per gestire sia la memoria di programma esistente, sia le dimensioni di eventuali aggiornamenti via etere (OTA). Alcuni sistemi possono richiedere tre volte lo spazio di memoria stimato per il programma, con la memoria aggiuntiva assegnata a un'immagine di sola lettura del firmware di fabbrica. In caso di alcuni tipi di guasti, tra cui il rilevamento di hacking o di un'immagine del firmware danneggiata, per ripristinarsi il sistema può caricare l'immagine iniziale del firmware di fabbrica.

Per alcune applicazioni questa espansione della memoria può superare rapidamente il limite di 1 Mbit della flash incorporata, rendendo necessaria un'espansione della memoria esterna. Tradizionalmente, la soluzione consisteva nell'aggiungere un chip esterno di memoria flash parallela. In questo modo vengono però utilizzati circa 36 pin esterni sui microcontroller, che altrimenti potrebbero essere utilizzati per l'I/O dell'applicazione. Inoltre comporta uno spreco dello spazio su scheda e il probabile aumento delle interferenze elettromagnetiche (EMI) dalla scheda.

Espansione della memoria di programma SPI

Oltre che con un bus parallelo, la memoria di programma può essere espansa anche utilizzando l'interfaccia periferica seriale (SPI). Mentre la SPI convenzionale utilizza una sola linea dati per le trasmissioni half-duplex a bit singolo, nel corso degli anni è arrivata a supportare linee dati doppie e quadruple, il che ha portato al corrispondente aumento della velocità di trasmissione dei dati. L'aumento è stato tale che è diventato pratico interfacciarsi con un chip flash SPI esterno di grande capacità.

Per le applicazioni di memoria di programma, una dual SPI o una quad SPI convenzionale utilizza una configurazione flash shadow in cui la memoria dati della flash esterna viene copiata in una memoria statica ad accesso casuale (SRAM) incorporata che viene mappata nello spazio di memoria del programma. A fronte del vantaggio di poter espandere facilmente la memoria del programma e di migliorare contemporaneamente la velocità di esecuzione grazie alla SRAM veloce, non va dimenticato che questa soluzione ha anche notevoli svantaggi. Poiché la SRAM interna è limitata, vi si accede in modalità paged, dato che la memoria flash viene scambiata con la SRAM interna in base alle esigenze. Per ridurre questo collo di bottiglia si può aumentare la SRAM su chip, ma dato che la SRAM è uno dei blocchi più costosi di qualsiasi semiconduttore, così facendo si aumenta notevolmente il costo del microcontroller.

XiP è un'evoluzione più recente della SPI. La SPI XiP permette alla CPU del microcontroller di eseguire il codice del firmware direttamente dalla flash SPI esterna. Aggiungendo una cache all'interfaccia SPI XiP si può ottenere un notevole incremento della velocità di esecuzione del programma.

La popolarità della SPI XiP ha portato alla recente espansione dell'interfaccia con otto linee dati. Questa interfaccia SPI XiP ottale ha innalzato il throughput tanto da renderlo molto più veloce - oltre 100 Mbit/s - rispetto all'esecuzione con la memoria flash su chip.

Rivoluzione della memoria SPI

Tutto ciò ci porta curiosamente indietro di 30 anni. Prendiamo un sistema con 1 Mbit di flash su chip e 32 Mbit di memoria flash di programma esterna a cui si accede tramite un'interfaccia SPI XiP ottale. La memoria del programma su chip è talmente esigua che è inevitabile chiedersi se è possibile eliminare la flash su chip del microcontroller mantenendo comunque un sistema economicamente valido.

Per molto tempo si è pensato che un sistema di fascia media con un microcontroller flash fosse in ogni caso più vantaggioso economicamente rispetto a uno con un microcontroller Flashless ma con un chip flash esterno. Questa convinzione è cambiata solo da poco.

Se si toglie la memoria flash su chip, il costo del microcontroller ovviamente diminuisce. Ma a un esame più attento si vede che, se la flash non serve più, si possono eliminare anche le funzioni della tecnologia di processo che sono utilizzate solo per la flash. Questo permette di ridurre i costi del processo di produzione, abbattendo fortemente quelli del microcontroller. È ritornato così in auge quello che una trentina di anni fa era chiamato "microcontroller ROMless". Oggi è detto Flashless.

(Re)introduzione ai microcontroller Flashless

Un microcontroller ad alte prestazioni che può sfruttare la velocità della memoria flash è MIMXRT1052DVL6B (RT1052) Flashless di NXP Semiconductors. RT1052 fa parte della famiglia dei processori i.MX RT1050 di NXP e si basa su un Arm® Cortex®-M7 a 600 MHz con 32 kB di cache di istruzioni e 32 kB di cache dei dati. La velocità di 600 MHz del clock si ottiene rimuovendo la flash e utilizzando una tecnologia di processo CMOS ad alta velocità che non è limitata dalla memoria flash interna. RT1052 ha una grande quantità di SRAM - 512 kB - che può essere partizionata per l'uso della memoria di programma o dei dati.

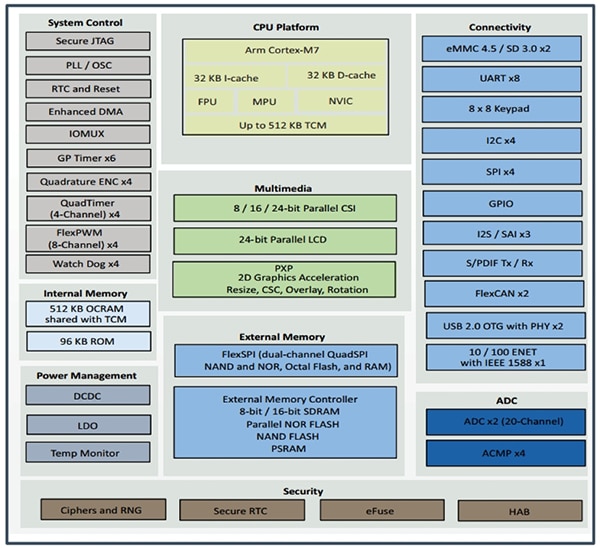

Il microcontroller dispone di numerose periferiche di fascia alta, tra cui un'interfaccia LCD, un'interfaccia sensore telecamera digitale (CSI) e Pixel Processing Pipeline (PXP) per il supporto telecamera di fascia alta, un'interfaccia SPDIF per audio digitale, due interfacce USB OTG, due interfacce flash card eMMC/SD, due convertitori analogico/digitale (ADC) a 20 canali e un modulo di crittografia. L'elenco completo delle periferiche è riportato nel diagramma a blocchi (Figura 1).

Figura 1: RT1052 di NXP ha un'ampia gamma di periferiche di fascia alta, fra cui un'interfaccia seriale SPI XiP e supporto per la crittografia dei dati. (Immagine per gentile concessione di NXP)

Figura 1: RT1052 di NXP ha un'ampia gamma di periferiche di fascia alta, fra cui un'interfaccia seriale SPI XiP e supporto per la crittografia dei dati. (Immagine per gentile concessione di NXP)

Un'altra opzione è rappresentata da MIMXRT1051DVL6B (RT1051) di NXP. Dispone di tutte le caratteristiche di RT1052, a parte l'interfaccia LCD, CSI e PXP.

RT1052 ha un'interfaccia FlexSPI in grado di eseguire il codice utilizzando interfacce flash SPI XiP dual, quad o ottali. Per una maggiore sicurezza firmware, il microcontroller supporta memoria di programma crittografata su SPI XiP, di cui ATXP032-CCUE-T di Adesto Technologies è un buon esempio.

Funzionamento della moderna flash XiP

ATXP032-CCUE-T di Adesto è un chip flash ottale a 32 Mbit che supporta trasferimenti dati fino a 266 Mbps in modalità DTR (Dual Transfer Rate) ottale, molto più rapida di quella flash su chip dei microcontroller. Richiede un'unica alimentazione di 1,8 V e ha una tipica corrente di standby in modalità ottale di 35 µA. Supporta un clock SPI massimo di 133 MHz.

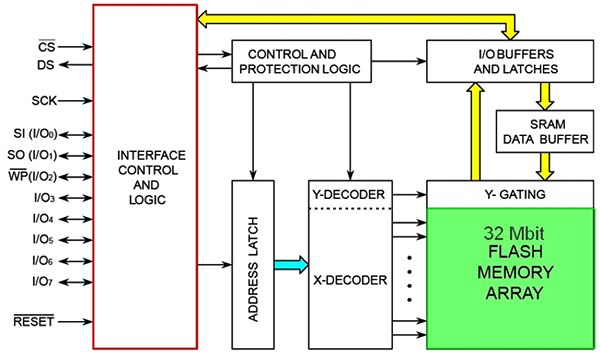

Figura 2: La memoria flash ATXP032-CCUE-T di Adesto usa una SPI ottale, da I/O0 a I/O7, per interfacciarsi con un microcontroller. Un buffer dei dati di scrittura SRAM migliora le prestazioni delle operazioni di scrittura su flash. (Immagine per gentile concessione di Adesto Technologies)

Figura 2: La memoria flash ATXP032-CCUE-T di Adesto usa una SPI ottale, da I/O0 a I/O7, per interfacciarsi con un microcontroller. Un buffer dei dati di scrittura SRAM migliora le prestazioni delle operazioni di scrittura su flash. (Immagine per gentile concessione di Adesto Technologies)

Durante una lettura della flash attiva, l'assorbimento di corrente di ATXP32 è di 142 µA/MHz più un sovraccarico di 1 milliampere (mA) (tipico). Alla velocità massima di 133 MHz in modalità ottale del suo clock SPI, assorbe solo 19,9 mA.

ATXP032-CCUE-T supporta anche le modalità standard SPI 0 e 3, oltre a quella quad SPI. Un registro di sicurezza a 256 byte ha un identificatore unico programmato in fabbrica a 128 byte, oltre a 128 byte di memoria a programmazione unica (OTP) che può essere utilizzata per memorizzare informazioni sul dispositivo, come un indirizzo MAC (Media Access Control) Ethernet o una chiave di sicurezza.

La disposizione della memoria di ATXP032-CCUE-T è degna di nota. È partizionata in quattro banchi di 8 Mbit l'uno. La logica interna è configurata in modo che un microcontroller host possa eseguire il codice da un banco mentre ne programma o ne cancella un altro. L'operazione è trasparente al microcontroller host e non richiede particolari impostazioni di configurazione.

ATXP032-CCUE-T dispone inoltre di tre registri di stato e di controllo per la configurazione dei parametri di funzionamento del dispositivo, come la modalità a basso consumo, l'abilitazione o disabilitazione della modalità DTR e l'impostazione delle modalità SPI standard, quad o ottale (quella predefinita è la modalità SPI standard). La lettura dei registri di stato può indicare lo stato di un programma o un'operazione di cancellazione, lo stato di basso consumo e se una parte della memoria è protetta in scrittura.

Combinazione di microcontroller Flashless e di XiP esterno

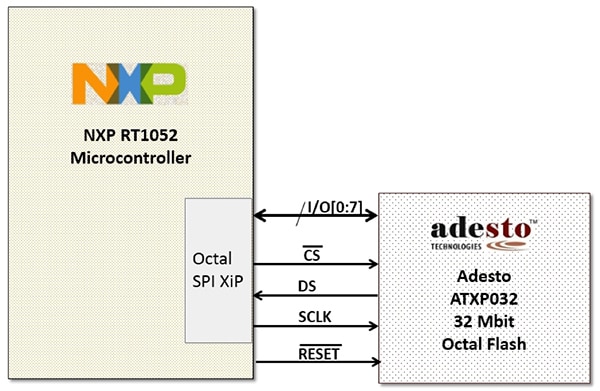

Combinare RT1052 e ATXP032-CCUE-T è estremamente semplice (Figura 3). All'accensione, RT1052 inizia a eseguire il codice dai 96 kB di ROM di boot su chip. La ROM di boot legge lo stato dei 14 pin di configurazione della modalità di avvio che selezionano quale delle numerose interfacce di memoria esterna di RT1052 utilizzare per la memoria di programma. Le opzioni includono una scheda eMMC esterna, una scheda micro SD, un'interfaccia parallela esterna convenzionale o la SPI XiP (in questo caso, ATXP032-CCUE-T di Adesto).

Figura 3: Il microcontroller Flashless RT1052 di NXP ha un'interfaccia SPI XiP ottale che può interfacciarsi facilmente con ATXP032-CCUE-T di Adesto. L'operazione di interfacciamento della SPI XiP ottale è trasparente al core Arm. (Immagine per gentile concessione di DigiKey)

Figura 3: Il microcontroller Flashless RT1052 di NXP ha un'interfaccia SPI XiP ottale che può interfacciarsi facilmente con ATXP032-CCUE-T di Adesto. L'operazione di interfacciamento della SPI XiP ottale è trasparente al core Arm. (Immagine per gentile concessione di DigiKey)

Le opzioni di boot di RT1052 includono anche il download del codice dalla USB OTG o una UART da eseguire dalla SRAM. Le opzioni della modalità di avvio possono essere impostate durante la produzione "bruciando" i registri "fuse" interni di RT1052 invece di utilizzare i pin di configurazione della modalità di avvio. Una volta abilitata l'interfaccia ottale SPI XiP per l'esecuzione della memoria di programma dalla ROM di boot di RT1052, l'esecuzione del programma è immediata. Il core Arm esegue quindi il firmware da ATXP032-CCUE-T di Adesto come da un dispositivo flash parallelo esterno o interno.

Trattandosi di trasferimenti di dati ad alta velocità, sulla scheda la flash seriale ottale dovrebbe essere posizionata il più vicino possibile alla porta SPI XiP ottale del microcontroller. Per ridurre le interferenze, nessuna delle tracce della scheda dovrebbe essere più lunga di 120 millimetri (mm). Per evitare interferenze, la distanza tra il segnale di clock e gli altri segnali dovrebbe essere pari ad almeno tre volte la larghezza delle tracce della scheda. Per evitare lo skew, i segnali dei dati bidirezionali di I/O [0:7] dovrebbero essere entro 10 mm l'uno dall'altro.

Conclusione

Le tendenze verso l'edge computing, la necessità di aggiornamenti OTA e le relative esigenze di scalabilità della memoria fanno sì che gli endpoint IoT abbiano bisogno di sempre più memoria. A un certo punto, i progettisti di questi dispositivi endpoint potrebbero prendere in considerazione l'uso di un microcontroller Flashless.

Come è stato dimostrato, i progressi dei microcontroller Flashless, delle interfacce ad alta velocità e dei chip flash SPI XiP ottali offrono la possibilità di realizzare endpoint IoT o sistemi embedded economici e ad alte prestazioni, invece di seguire gli approcci tradizionali con microcontroller basati su flash.

Esonero della responsabilità: le opinioni, le convinzioni e i punti di vista espressi dai vari autori e/o dai partecipanti al forum su questo sito Web non riflettono necessariamente le opinioni, le convinzioni e i punti di vista di DigiKey o le sue politiche.