Utilizzo di componenti pronti per l'uso per generare sequenze binarie pseudocasuali e rumore bianco

Contributo di Editori nordamericani di DigiKey

2018-03-22

Anche se segnali casuali come il rumore spesso sono considerati un problema, esistono applicazioni di comunicazione e test dei dispositivi che dipendono da sequenze di bit casuali e dal rumore, a causa delle loro caratteristiche uniche. Tuttavia, per prove eccezionali o se il progettista ha un budget limitato, potrebbe non essere possibile acquistare una sequenza binaria pseudocasuale (PRBS) o un generatore di forme d'onda arbitrarie realizzati appositamente per tale scopo. In questi casi è più conveniente crearne una utilizzando dispositivi CMOS facilmente reperibili.

Questo articolo descriverà i ruoli utili della PRBS e del rumore nell'elettronica. Presenterà quindi i circuiti integrati CMOS facilmente reperibili e mostrerà come possono essere utilizzati per generare il rumore pseudocasuale e le sequenze binarie richieste.

Il ruolo del rumore "buono"

Il rumore bianco, casuale, ha uno spettro piatto nel dominio della frequenza. Lo spettro di ampiezza dell'uscita medio di un amplificatore o di un filtro eccitato da una sorgente di rumore bianco fornirà la risposta in frequenza di ampiezza di quel dispositivo.

Nelle comunicazioni, un flusso di dati per un trasmettitore CDMA viene moltiplicato per una sequenza binaria pseudocasuale (PRBS). Può quindi essere trasmesso sullo stesso canale RF di molti altri segnali. Correlando il segnale composito con la stessa PRBS dal lato del ricevitore si estrae il flusso di dati originale con un'interferenza minima o nulla. Dato che questi segnali casuali sono così utili, è importante poterli generare quando serve.

Generazione di una PRBS

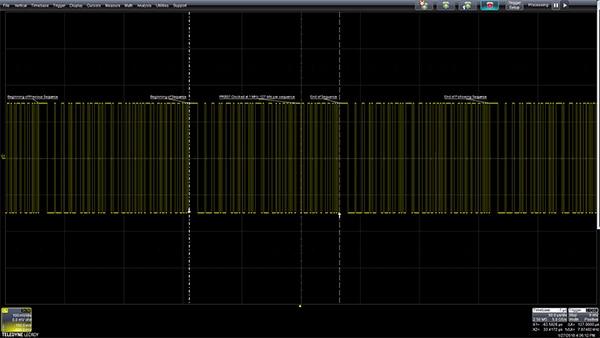

Una PRBS è un segnale deterministico periodico costituito da una serie di uno e zeri digitali. La durata dei livelli uno o zero è un multiplo del periodo di clock del generatore di PRBS. La sequenza di cifre uno e zero è casuale all'interno del periodo di ripetizione del generatore (Figura 1).

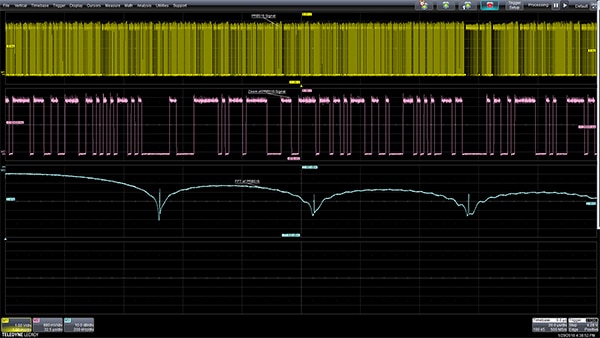

Figura 1: Un segnale PRBS7 è un segnale di test PRBS con una lunghezza di 7 bit che ha un periodo di 27 – 1 o 127 bit. Questo segnale ha un clock a 1 MHz e mostra una periodicità di 127 ms, come indicato dai cursori dell'oscilloscopio. (Immagine per gentile concessione di DigiKey)

Il segnale in Figura 1 è un segnale di test PRBS7 che contiene 127 bit in ogni periodo della sequenza e viene prodotto da un generatore a 7 stadi. All'interno di ogni periodo la sequenza di bit è casuale, ma l'intera sequenza si ripete in modo identico ogni 127 periodi di clock.

Questi segnali di test possono essere generati nel software o nell'hardware. Il vantaggio di un'implementazione hardware per il test è che i segnali sono disponibili esternamente per pilotare il dispositivo da testare.

Registro a scorrimento a retroazione lineare

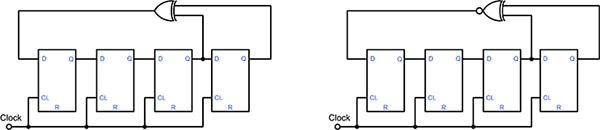

L'implementazione hardware di una PRBS viene fatta utilizzando dei registri a scorrimento a retroazione lineare (LFSR). Alcuni registri a scorrimento sono disposti in serie con la retroazione dagli stadi successivi indietro verso l'ingresso, utilizzando gate EXCLUSIVE-OR/NOR. Il numero di registri a scorrimento usati determina la lunghezza o durata della sequenza (Figura 2).

Figura 2: Esempi di una LFSR a quattro bit implementata con logica di retroazione sia esclusiva OR che esclusiva NOR. I tap di retroazione determinano la sequenza degli stati dei dati. (Immagine per gentile concessione di DigiKey)

Sebbene siano possibili molte configurazioni di retroazione, quasi tutti i progetti utilizzano tap che producono sequenze di lunghezze massime, così che il numero totale di stati sia uguale a (2N-1), dove N è il numero di stadi del registro a scorrimento. La Tabella 1 riassume i tap per sequenze di lunghezza massima per lunghezze LFSR da 2 a 32. Questi tap non sono esclusivi. Tenere presente che può esistere più di un polinomio di lunghezza massima per una qualsiasi lunghezza del registro a scorrimento.

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Tabella 1: Riepilogo dei tap per sequenze di lunghezza massima per lunghezze LFSR da 2 a 32. (Immagine per gentile concessione di DigiKey)

Il nostro esempio usa una LFSR a 15 stadi che produce una sequenza casuale lunga 32.767 bit, nota come sequenza di test PRBS15. Sequenze più lunghe le si può ottenere con una LFSR con un maggior numero di stadi. La limitazione che comporta l'uso di una sequenza di test PRBS è rappresentata dalla durata del test. Una sequenza di 15 bit con clock a 500 kHz richiede 65 millisecondi (ms). Una sequenza di 31 bit richiederebbe 4295 secondi, o circa 72 minuti.

L'esempio nella Figura 2 utilizza quattro registri a scorrimento per produrre sequenze di dati con 15 stati distinti. Si noti che entrambe le configurazioni hanno un unico stato proibito. Nel caso del modello di retroazione OR esclusivo, lo stato "tutti zeri" non viene utilizzato perché, una volta caricato, il registro a scorrimento rimarrebbe bloccato in quello stato. Allo stesso modo, tutti gli stati uno sono vietati nell'implementazione NOR esclusivo. Le Tabelle 2 e 3 mostrano le sequenze di dati di entrambe le configurazioni per l'LFSR a quattro bit, utilizzando i tap di retroazione degli stadi tre e quattro.

|

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Tabella 2 e 3: Pattern di dati per configurazioni OR e NOR illustrate nella Figura 1. (Immagine per gentile concessione di DigiKey)

Entrambe le implementazioni partono da uno stato noto, tutti uno nel caso OR e tutti zeri nel caso NOR. Le LFSR a quattro bit di lunghezza massima forniscono 15 stati possibili (2N-1) come mostrato nelle tabelle.

La sequenza dei dati di uscita è periodica, poiché si ripete dopo 15 clock. È anche deterministica, in quanto è possibile prevedere il risultato per una determinata configurazione e stato iniziale noto. La sequenza risultante è tuttavia casuale entro il periodo di 15 clock.

Progettazione di un generatore di sequenza binaria pseudocasuale

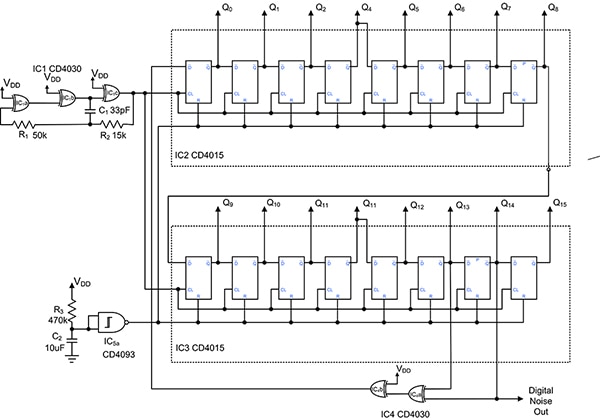

Il progetto di un generatore PRBS pratico e a basso costo, basato sull'implementazione LFSR tramite il doppio registro a scorrimento statico a 4 stadi CD4015BM96 di Texas Instruments e lo XOR a 4 gate CD4030BM96 è illustrato in Figura 3.

Figura 3: Schema semplificato del generatore PRBS15 utilizzando il doppio registro a scorrimento statico a 4 stadi CD4015BM96 di Texas Instruments e lo XOR a 4 gate CD4030BM96 (Immagine per gentile concessione di DigiKey)

Questo generatore usa 16 flip-flop di tipo D (otto per CI) con tap di retroazione sul 14° e 15° producendo una sequenza di dati PRBS15. La connessione di retroazione avviene tramite un gate XOR che viene poi invertito per formare una LFSR configurata XNOR. Questa sequenza di dati ha una lunghezza di 32.767 bit che corrisponde a una durata di circa 65 ms ad una frequenza di clock di 500 kHz. Per ottenere sequenze più lunghe si possono utilizzare registri a scorrimento più lunghi con un cambiamento appropriato nei tap di retroazione. L'estensione del progetto a una sequenza a 31 bit aumenta la durata della sequenza a oltre 2 miliardi di stati (circa 72 minuti a una frequenza di clock di 500 kHz).

Il generatore viene inizializzato allo stato tutti zeri all'accensione utilizzando un gate NAND a trigger di Schmitt CD4093BM96 (IC5) e una semplice rete RC. Il clock è fornito da un semplice oscillatore CMOS che opera attorno ai 500 kHz. L'uscita digitale può essere prelevata da una qualsiasi delle uscite Q del registro a scorrimento. In questo caso è stata usata Q14.

L'uscita del generatore e la trasformata di Fourier veloce (FFT) dell'uscita vengono visualizzate su un oscilloscopio in Figura 4.

Figura 4: L'uscita del generatore (traccia superiore) viene espansa orizzontalmente nella traccia centrale per vedere la struttura dettagliata. La FFT del rumore digitale mostra la risposta sin(x)/x attesa di una forma d'onda pulsata con zeri ai multipli della frequenza di clock. (Immagine per gentile concessione di DigiKey)

La FFT del rumore digitale mostra la risposta sin(x)/x attesa di una forma d'onda pulsata con zeri ai multipli della frequenza di clock. Lo spettro è abbastanza piatto fino a circa il 10% della frequenza di clock. Questa è la chiave per estrarre il rumore bianco dall'uscita digitale utilizzando un filtro passa-basso.

Generatore di rumore bianco

È detto rumore bianco un rumore che è spettralmente piatto sul suo spettro delle frequenze. La densità spettrale della potenza e la potenza per larghezza di banda unitaria sono costanti sulla larghezza di banda del rumore. Filtrando l'uscita del rumore digitale, il generatore di PRBS produrrà rumore bianco.

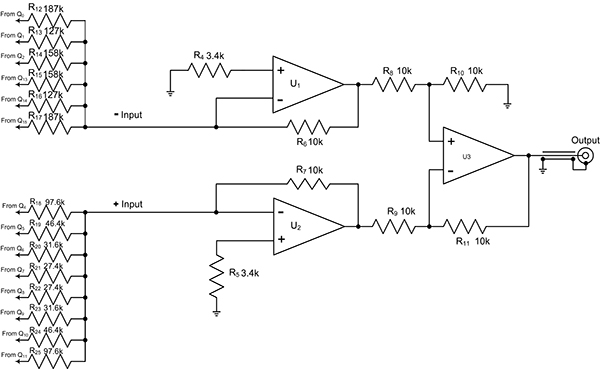

Anche se si potrebbe usare un filtro analogico, sarebbe limitato a una specifica frequenza di clock. Utilizzando un filtro digitale passa-basso a risposta di impulso finita (FIR), il taglio del filtro tiene traccia di qualsiasi variazione della frequenza di clock. Inoltre, il filtro FIR può fornire frequenze di taglio molto basse che richiederebbero condensatori molto grandi in un filtro analogico. Il filtro FIR combina la somma ponderata delle uscite del registro a scorrimento. La ponderazione necessaria per produrre una risposta del filtro passa-basso rettangolare nel dominio della frequenza è sin(x)/x nel dominio temporale (Figura 5).

Figura 5: Lo stadio di uscita del generatore utilizza campioni ponderati sin(x)/x dalle uscite del registro a scorrimento per implementare un filtro passa-basso FIR. Dato che la ponderazione sin(x)/x richiede termini negativi, per sommare i componenti ponderati positivi e negativi viene utilizzato un amplificatore differenziale. (Immagine per gentile concessione di DigiKey)

Le uscite del registro a scorrimento ponderate vengono sommate nell'amplificatore differenziale, che è costruito utilizzando tre sezioni di un amplificatore operazionale quadruplo LM324KDR. Il banco del resistore superiore rappresenta i componenti negativi della ponderazione sin(x)/x. Il banco del resistore inferiore rappresenta i valori positivi. Le uscite Q3 e Q12 non sono collegate perché rappresentano i punti zero-crossing della funzione sin(x)/x. L'uscita risultante del rumore bianco presenta la classica funzione gaussiana di densità della probabilità (PDF) (Figura 6).

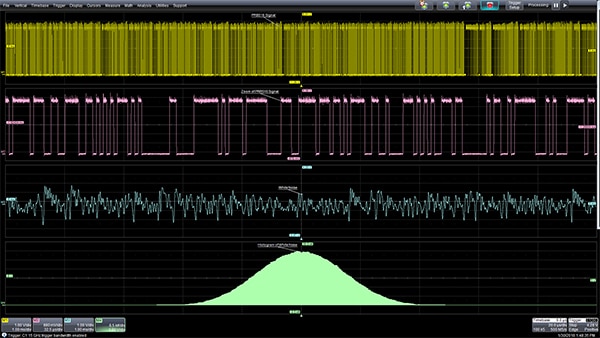

Figura: Rumore digitale PRBS (due tracce superiori) assieme all'uscita del rumore bianco analogica (terza traccia dall'alto). L'istogramma del rumore bianco, traccia inferiore, espone il PDF gaussiano classico o quello normale a forma di campana. (Immagine per gentile concessione di DigiKey)

Il segnale del rumore bianco è il terzo dall'alto verso il basso. Di seguito è riportato l'istogramma del rumore che mostra la distribuzione di probabilità normale o gaussiana attesa. La banda del rumore bianco è limitata al 5% della frequenza di clock, o 25 kHz, che è adatta per test di frequenza audio.

Conclusione

Come mostrato, i circuiti integrati CMOS facilmente reperibili possono essere utilizzati per produrre sia una sequenza binaria pseudocasuale, sia rumore bianco analogico a fini di comunicazioni e test. La distinta base per le parti usate è poco costosa, e quindi ideale per ricerche accademiche, hobbisti e tecnici e ingegneri attenti all'economia.

Esonero della responsabilità: le opinioni, le convinzioni e i punti di vista espressi dai vari autori e/o dai partecipanti al forum su questo sito Web non riflettono necessariamente le opinioni, le convinzioni e i punti di vista di DigiKey o le sue politiche.