Utilizzare MOSFET basati su SiC per migliorare l'efficienza di conversione di potenza

Contributo di Editori nordamericani di DigiKey

2019-10-29

L'affermarsi di requisiti di potenza più elevati, gli obblighi normativi e gli standard sul risparmio energetico e sulle problematiche EMI stanno imponendo l'utilizzo di dispositivi di potenza a commutazione per gli alimentatori, in considerazione della loro maggior efficienza e dell'intervallo di funzionamento più ampio. Contemporaneamente, i progettisti sono sottoposti a una costante pressione verso la riduzione dei costi e il risparmio di spazio. Alla luce di ciò, serve un'alternativa ai classici MOSFET a base di silicio (Si).

Il carburo di silicio (SiC) rappresenta una valida alternativa, ora che è una tecnologia matura di terza generazione. I FET a base di carburo di silicio offrono molti vantaggi, in particolare per ciò che concerne l'efficienza, la maggiore affidabilità, la riduzione dei problemi di gestione termica e un ingombro ridotto. Sono applicabili all'intero spettro di potenza e non costringono a un mutamento radicale delle tecniche di progettazione, sebbene possano richiedere qualche adattamento.

In questo articolo metteremo velocemente a confronto il silicio (Si) con il carburo di silicio (SiC), proporremo esempi di dispositivi al carburo di silicio di Cree/Wolfspeed e spiegheremo come iniziare a utilizzarli nella progettazione.

MOSFET in Si e in SiC a confronto

Innanzitutto occorre fare chiarezza sulla tecnologia e sulla terminologia; i FET a base di carburo di silicio sono MOSFET, proprio come i loro predecessori in silicio. In senso ampio, le loro strutture fisiche interne sono simili e si tratta in entrambi i casi di dispositivi a tre terminali con collegamenti alla sorgente, al drain e al gate.

La differenza tra loro è quella indicata dal nome: i FET in SiC utilizzano il carburo di silicio come materiale base al posto del solo silicio. Molti operatori del settore li chiamano "dispositivi in SiC" senza menzionare "MOSFET". In questo articolo li chiameremo FET in SiC.

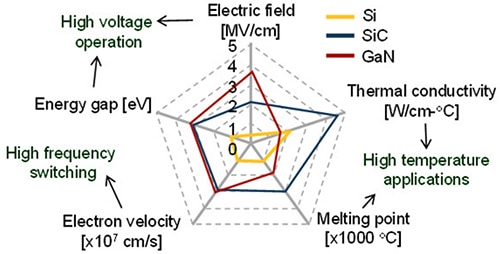

Perché utilizzare un composto a base di carburo di silicio come materiale? Per ragioni di natura fisica, il SiC ha tre proprietà elettriche fondamentali che differiscono in modo significativo da quelle del silicio, ciascuna delle quali offre vantaggi operativi; ma ve ne sono anche di più sottili (Figura 1).

Figura 1: Confronto approssimativo tra le principali proprietà materiali del SiC e quelle dei materiali solidi Si e GaN. A confronto del Si, il SiC ha livelli più alti di cedimento critico, di conducibilità termica e una banda proibita più ampia. (Immagine per gentile concessione di Researchgate)

Figura 1: Confronto approssimativo tra le principali proprietà materiali del SiC e quelle dei materiali solidi Si e GaN. A confronto del Si, il SiC ha livelli più alti di cedimento critico, di conducibilità termica e una banda proibita più ampia. (Immagine per gentile concessione di Researchgate)

Parliamo di:

- Valori più alti per la tensione critica di rottura del campo elettrico, pari a circa 2,8 megavolt al centimetro (MV/cm) a fronte di 0,3 MV/cm; il funzionamento a una determinata tensione nominale richiede pertanto uno strato molto più sottile, con la conseguente riduzione della resistenza nello stato On.

- Maggiore conducibilità termica, che consente una densità di corrente più elevata in un'area con sezione trasversale.

- Banda proibita più larga (la differenza di energia (in eV) tra la parte superiore della banda di valenza e il fondo della banda di conduzione nei semiconduttori (e isolatori)) che determina una corrente di dispersione più bassa alle alte temperature. È per questa ragione che i diodi e i FET in Sic sono spesso chiamati "dispositivi ad ampia banda proibita" (WBG).

Di conseguenza, in termini approssimativi, i dispositivi in SiC sono in grado di bloccare tensioni sino a dieci volte superiori rispetto a quelli in silicio e possono commutare dieci volte più velocemente con una resistenza nello stato On pari alla metà o meno a 25 °C. Al contempo, la loro capacità di funzionare a temperature di ben lunga superiori ai 200°°C rispetto ai 125°°C semplifica la progettazione e la gestione termica.

Il ruolo critico dei gate driver per ottenere i benefici

Un dispositivo di potenza non funziona senza il suo gate driver, che traduce segnali di controllo digitali di basso livello nei segnali di corrente e tensione necessari oltre a fornire la temporizzazione necessaria al dispositivo di potenza (offrendo inoltre un certo grado di protezione nei confronti della maggior parte dei guasti esterni). Per i FET in SiC, il driver deve avere altre funzioni per poter:

- Ridurre al minimo le perdite di conduzione e commutazione nonché le perdite del gate. Esse comprendono l'energia di attivazione e disattivazione, l'effetto di Miller e i requisiti per la corrente di comando del gate. L'energia di disattivazione è una funzione della resistenza del gate e della tensione gate-sorgente nello stato off. Per ridurle, è necessario che dal gate venga rimossa più corrente. Uno dei modo per farlo consiste nell'applicazione da parte del driver di una polarizzazione negativa alla tensione del gate durante il tempo di disattivazione. Analogamente, l'energia di attivazione viene ridotta diminuendo la resistenza del gate.

- Ridurre al minimo l'effetto di Miller e le sue conseguenze negative, cioè la possibile attivazione involontaria causata dalla capacità parassita in alcune circostanze e configurazioni applicative. L'attivazione indotta dall'effetto Miller aumenta l'energia di recupero inverso e si aggiunge alle perdite. Una soluzione consiste nel dotare il driver della cosiddetta funzione di protezione Miller Clamp, che controlla la corrente di comando durante la commutazione dello stadio di potenza.

- Fornire la corrente di sink e di source necessaria a valori di tensione idonei. I dispositivi in SiC in genere necessitano di un pilotaggio del gate con polarizzazione positiva più alta (+20 V) rispetto ai MOSFET in silicio per ridurre al minimo le perdite; possono anche richiedere una tensione di disattivazione del gate negativa compresa tra -2 e -6 V. La tensione di gate necessaria viene stabilita con i soliti calcoli che si basano su carica del gate (Qg), VDD, ID della corrente di drain, tensione gate-source e resistenza del gate ed è in genere nell'ordine di pochi ampere. Questa corrente deve avere valori nominali di sink e di source adeguati a una velocità di variazione commisurata alla velocità di commutazione del FET in SiC.

- Modellare e ridurre al minimo le correnti parassite della scheda e del dispositivo (sia le induttanze parassite sia le capacitanze) che possono produrre oscillazione, sovraelongazione di tensione/corrente e falsi positivi alle velocità di commutazione più alte offerte da questi dispositivi. I MOSFET in silicio hanno una piccola "coda" di corrente che agisce come smorzatore o soppressore per ridurre in qualche misura la sovraelongazione e la sovraoscillazione. I MOSFET in SiC non hanno questa coda, perciò la sovraelongazione e la sovraoscillazione della tensione di drain possono essere elevate, dando origine a problemi. La diminuzione di queste correnti parassite richiede grande attenzione alle problematiche di layout, con la riduzione al minimo delle lunghezze dei conduttori e la collocazione del driver il più vicino possibile al proprio dispositivo di potenza. Persino pochi centimetri possono fare la differenza, in quanto gli effetti di queste induttanze parassite e capacitanze diventano più pronunciati in presenza delle più alte velocità di commutazione offerte dai FET in SiC. La riduzione della sovraoscillazione porta con sé anche un altro vantaggio, visto che riduce la generazione delle EMI associate alla commutazione ad alta velocità sia lato pilotaggio sia lato carico del dispositivo.

Nonostante le ulteriori problematiche poste dal pilotaggio dei MOSFET in SiC, molti fornitori propongono CI standard progettati a questo scopo, dotati di caratteristiche che ben si sposano alle esigenze specifiche dei dispositivi in SiC. Occorre notare che in molti progetti i gate driver e i FET in SiC devono possedere un isolamento galvanico dalla circuiteria di bassa tensione, che può essere implementato tramite tecniche di isolamento ottico, trasformatore di impulsi o isolamento capacitivo utilizzando componenti standard. L'isolamento in primo luogo ha come scopo la sicurezza degli utenti, che devono essere protetti dalle alte tensioni in caso di malfunzionamento del circuiti, e in secondo luogo nelle varie topologie di circuito dove il MOSFET è intrinsecamente non a massa, come nelle configurazioni a ponte.

I nuovi dispositivi danno prova di buone prestazioni

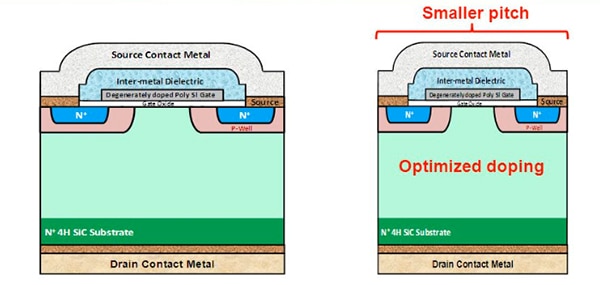

Il primo MOSEFT in SiC a scopo commerciale, il CMF20120D, è stato realizzato da Cree/Wolfspeed nel gennaio del 2011 (Wolfspeed è la divisione di Cree che si occupa di alimentazione e radiofrequenza, il cui nome è stato reso noto nel 2015); i wafer in SiC erano disponibili da qualche anno. Aveva una capacità nominale di 1200 V/98 A con 80°mΩ di resistenza nello stato On (valori riferiti a 25 °C), ed era confezionato in un contenitore TO-247. CREE ha proposto poco dopo un processo di 2a generazione e attualmente è arrivata alla 3a generazione di MOSEFT in SiC, denominati dispositivi C3M (Figura 2).

Figura 2: Il confronto tra la struttura del processo per la 2a (a sinistra) e la 3a (a destra) generazione di SiC di Cree mostra differenze di modesta entità, ma da queste sezioni trasversali non emerge il miglioramento che si ottiene nelle specifiche prestazionali. (Immagine per gentile concessione di Cree/Wolfspeed)

Figura 2: Il confronto tra la struttura del processo per la 2a (a sinistra) e la 3a (a destra) generazione di SiC di Cree mostra differenze di modesta entità, ma da queste sezioni trasversali non emerge il miglioramento che si ottiene nelle specifiche prestazionali. (Immagine per gentile concessione di Cree/Wolfspeed)

Ad esempio, tra i membri della prima piattaforma di MOSFET in SiC da 900 V del settore troviamo C3M0280090J. È ottimizzato per le applicazioni dell'elettronica di potenza ad alta frequenza, tra cui gli inverter a energia rinnovabile, i sistemi di carica dei veicoli elettrici e gli alimentatori trifase industriali (Tabella 1).

|

Tabella 1: Le proprietà di primo livello del MOSFET in SiC C3M0280090J di Cree ne indicano l'adeguatezza agli inverter a energia rinnovabile, ai sistemi di carica dei veicoli elettrici e agli alimentatori trifase industriali. (Tabella per gentile concessione di Cree/Wolfspeed)

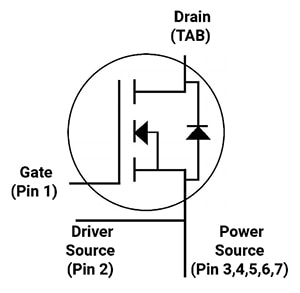

Oltre alle specifiche di tensione/corrente, questo dispositivo è ottimizzato per la commutazione ad alta velocità con bassa capacità elettrica, ha un contenitore a bassa impedenza con un collegamento alla sorgente di pilotaggio (Figura 3), contiene un diodo intrinseco veloce con una bassa carica di recupero inverso (Qrr) e ha un ampio isolamento superficiale (~7°mm) tra drain e sorgente.

Figura 3: C3M0280090J di Cree ha un contenitore a bassa impedenza con un collegamento alla sorgente di pilotaggio. (Immagine per gentile concessione di Cree/Wolfspeed)

Figura 3: C3M0280090J di Cree ha un contenitore a bassa impedenza con un collegamento alla sorgente di pilotaggio. (Immagine per gentile concessione di Cree/Wolfspeed)

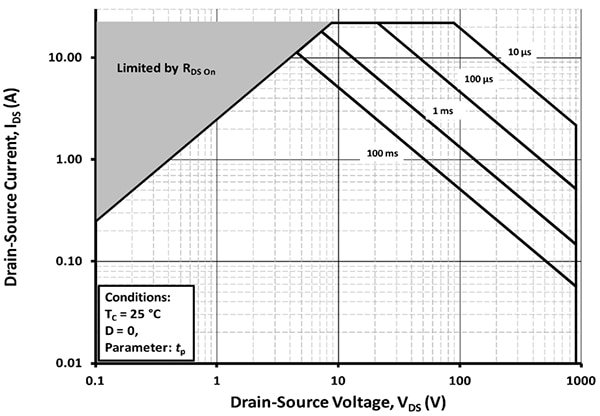

Questa piattaforma da 900 V si presta alla realizzazione di sistemi di conversione della potenza di prossima generazione, più piccoli e dotati di maggiore efficienza, agli stessi costi delle soluzioni basate sul silicio ma dotati di specifiche di livello superiore. Il grafico dell'area operativa sicura (SOA) riassume le caratteristiche di questo FET in SiC (Figura 4). Quando la tensione drain/source (VDS) è bassa, la corrente massima è limitata dalla resistenza nello stato On; e a valori moderati di VDS il componente può reggere 15 A per brevi periodi di tempo.

Figura 4: Il grafico della SOA per il C3M0280090J di Cree mostra le sue caratteristiche IDS a confronto con quelle VDS. (Immagine per gentile concessione di Cree/Wolfspeed)

Figura 4: Il grafico della SOA per il C3M0280090J di Cree mostra le sue caratteristiche IDS a confronto con quelle VDS. (Immagine per gentile concessione di Cree/Wolfspeed)

Il confezionamento influisce sulle prestazioni

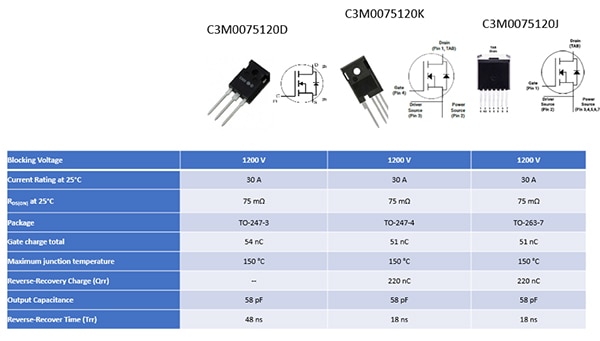

CREE propone inoltre tre dispositivi con specifiche simili: C3M0075120D, C3M0075120K e C3M0075120J, che differiscono principalmente riguardo al contenitore (Figura 5).

Figura 5: Cree offre lo stesso FET in SiC da 1200 V in 3 contenitori con specifiche grosso modo simili ma non identiche. (Immagine per gentile concessione di Cree/Wolfspeed)

Figura 5: Cree offre lo stesso FET in SiC da 1200 V in 3 contenitori con specifiche grosso modo simili ma non identiche. (Immagine per gentile concessione di Cree/Wolfspeed)

Ma c'è altro al di là dei numeri. Il dispositivo con suffisso D ha un contenitore a tre terminali (TO-247-3), mentre quello con il suffisso K ha un contenitore a quattro terminali (TO-247-4). Questi due dispositivi, così come il dispositivo a sette terminali con suffisso J, contengono un pin sorgente Kelvin che riduce l'effetto dei picchi di tensione indotti di L × di/dt nel circuito del gate. Pertanto è possibile applicare più tensione al gate e alla sorgente ottenendo una commutazione dinamica più veloce. I risultati mostrano una potenziale riduzione delle perdite di commutazione di 3,5 volte quando i dispositivi vengono misurati in prossimità della corrente nominale.

Le schede di valutazione e i progetti di riferimento portano più velocemente al risultato

Sebbene ci troviamo sul lato opposto dello spettro rispetto ai progetti RF con frequenza in gigahertz, la creazione di un circuito ad alte prestazioni per il funzionamento a tensioni e intervalli di potenza più elevati richiede comunque una certa attenzione ai particolari. Ogni piccolo dettaglio e idiosincrasia dei componenti e del layout vengono ingigantiti e il circuito fisico non perdona la benché minima trascuratezza.

Per aiutare i progettisti a verificare le prestazioni di commutazione ad alta velocità di FET in SiC come C3M0075120D e C3M0075120K, Cree propone il kit di valutazione buck-boost KIT-CRD-3DD12P (Figura 6). Il kit è in grado di gestire sia il contenitore a tre terminali di C3M0075120D sia il contenitore a quattro terminali di C3M0075120K, identico sotto tutti gli altri aspetti. In questo modo il progettista può collaudare e confrontare le prestazioni dei MOSFET di terza generazione (C3M) di Cree/Wolfspeed in diversi contenitori.

Figura 6: Il kit di valutazione CRD-3DD12P fornisce un utile metodo per verificare le prestazioni sia di C3M0075120D a tre terminali nel contenitore TO-247 sia di C3M0075120K a quattro terminali. Da notare il grande dissipatore di calore e l'induttore toroidale che rendono possibili prestazioni termiche di eccellente livello. (Immagine per gentile concessione di Cree/Wolfspeed)

Figura 6: Il kit di valutazione CRD-3DD12P fornisce un utile metodo per verificare le prestazioni sia di C3M0075120D a tre terminali nel contenitore TO-247 sia di C3M0075120K a quattro terminali. Da notare il grande dissipatore di calore e l'induttore toroidale che rendono possibili prestazioni termiche di eccellente livello. (Immagine per gentile concessione di Cree/Wolfspeed)

Il kit di valutazione viene proposto in una configurazione a semiponte e consente l'aggiunta di un MOSFET o di un diodo nella posizione superiore e inferiore, in modo tale che la scheda possa avere topologie di conversione di potenza comuni come il buck sincrono o il boost sincrono. Consente inoltre l'aggiunta di diodi o sopra o sul fondo, perché gli utenti possano valutare la topologia di convertitori buck o boost asincroni.

Inoltre, per ridurre la perdita di potenza il kit viene offerto con un induttore a bassa perdita realizzato in sendust. Questa polvere magnetica di metallo, conosciuta anche come Kool Mµ e composta all'85% di ferro, 9% di silicio e 6% di alluminio, viene utilizzata come alternativa al permalloy in virtù delle sue migliori specifiche per i parametri fondamentali in campo magnetico e termico.

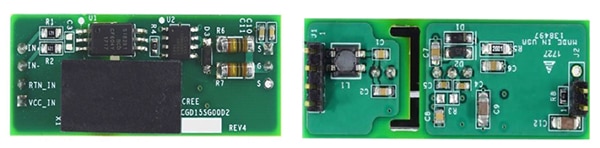

A coloro che desiderano progettare il proprio sottocircuito di pilotaggio del gate, Cree/Wolfspeed propone anche il progetto di riferimento CGD15SG00D2 del gate driver per questi FET in SiC di 3a generazione (Figura 7).

Figura 7: La parte superiore (sinistra) e inferiore (destra) del progetto di riferimento CGD15SG00D2 del gate driver: una scheda completa con una distinta base finita nonché la predisposizione per la valutazione delle prestazioni del contenitore TO-247 a tre conduttori rispetto a quello a quattro con lo stesso die MOSFET in SiC. (Immagine per gentile concessione di Cree/Wolfspeed)

Figura 7: La parte superiore (sinistra) e inferiore (destra) del progetto di riferimento CGD15SG00D2 del gate driver: una scheda completa con una distinta base finita nonché la predisposizione per la valutazione delle prestazioni del contenitore TO-247 a tre conduttori rispetto a quello a quattro con lo stesso die MOSFET in SiC. (Immagine per gentile concessione di Cree/Wolfspeed)

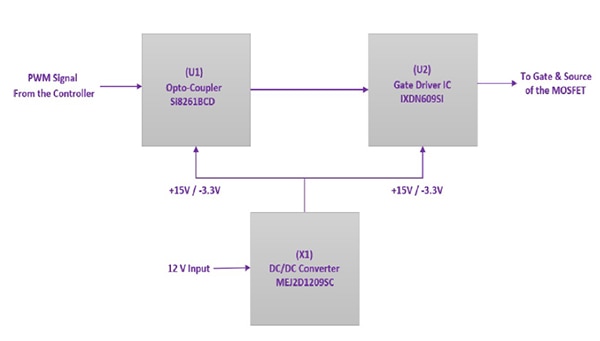

Il diagramma a blocchi di alto livello (Figura 8) di CGD15SG00D2 illustra le funzioni di questo progetto di riferimento, incluso l'optoaccoppiatore (U1), il circuito integrato del gate driver (U2) e l'alimentatore isolato (X1). L'optoaccoppiatore (isolamento a 5.000 V c.a.) accetta segnali di modulazione della larghezza di impulso (PWM) e fornisce immunità di modo comune di 35/50 kV/µs (valore minimo/tipico). Tra le altre caratteristiche degne di nota, segnaliamo:

- Una scanalatura che ottimizza le specifiche obbligatorie di isolamento superficiale tra il lato logico e il lato potenza del circuito stampato e una scanalatura che ottimizza l'isolamento superficiale tra i circuiti primario e secondario della scheda.

- Un alimentatore isolato da 2 V che supporta il funzionamento di MOSFET più grandi a frequenze più alte.

- Resistori separati per l'attivazione e la disattivazione del gate con un diodo dedicato per consentire all'utente di personalizzare e ottimizzare sia i segnali di attivazione sia quelli di disattivazione.

- Un induttore in modo comune sull'ingresso di alimentazione della logica per l'ottimizzazione dell'immunità EMI.

Figura 8: In questo diagramma a blocchi di alto livello del progetto di riferimento CGD15SG00D2 del gate driver si vedono i suoi blocchi funzionali principali: l'optoaccoppiatore U1, il gate driver in CI U2 e l'alimentatore isolato X1. (Immagine per gentile concessione di Cree/Wolfspeed)

Figura 8: In questo diagramma a blocchi di alto livello del progetto di riferimento CGD15SG00D2 del gate driver si vedono i suoi blocchi funzionali principali: l'optoaccoppiatore U1, il gate driver in CI U2 e l'alimentatore isolato X1. (Immagine per gentile concessione di Cree/Wolfspeed)

Conclusione

I MOSFET in SiC di terza generazione di Cree/Wolfspeed offrono significativi vantaggi in termini di efficienza e di prestazioni termiche per le applicazioni di commutazione di potenza rispetto ai tradizionali MOSFET in Si. Se abbinati a un driver idoneo offrono prestazioni affidabili e uniformi sia nelle applicazioni già affermate sia in quelle emergenti.

Esonero della responsabilità: le opinioni, le convinzioni e i punti di vista espressi dai vari autori e/o dai partecipanti al forum su questo sito Web non riflettono necessariamente le opinioni, le convinzioni e i punti di vista di DigiKey o le sue politiche.