Utilizzare gli FPGA per costruire applicazioni Edge IA ad alte prestazioni e alta efficienza energetica

Contributo di Editori nordamericani di DigiKey

2021-01-12

I progettisti che desiderano implementare gli algoritmi di intelligenza artificiale (IA) su processori di inferenza sull'edge sono sotto la costante pressione di ridurre il consumo energetico e i tempi di sviluppo, nonostante le esigenze di elaborazione aumentino. Gli array di porte programmabili sul campo (FPGA) offrono una combinazione particolarmente efficace di velocità ed efficienza energetica per l'implementazione dei motori di inferenza di reti neurali (NN) necessari per l'Edge IA. Per gli sviluppatori che non hanno familiarità con gli FPGA, tuttavia, i metodi di sviluppo convenzionali possono sembrare complessi, spesso inducendoli a rivolgersi a soluzioni meno che ottimali.

Questo articolo descrive un approccio più semplice, proposto da Microchip Technology, che consente agli sviluppatori di aggirare i processi di sviluppo tradizionali per creare NN addestrate utilizzando un FPGA e un kit di sviluppo software (SDK) oppure utilizzando un kit video basato su FPGA per passare immediatamente allo sviluppo di applicazioni di visione embedded intelligenti.

Perché usare l'Edge IA?

L'edge computing apporta una serie di vantaggi alle applicazioni Internet delle cose (IoT) in segmenti diversificati come l'automazione industriale, i sistemi di sicurezza, la domotica e molti altri. In un'applicazione di IoT industriale (IIoT) rivolta al settore industriale, l'edge computing può migliorare drasticamente i tempi di risposta nei cicli di controllo di processo eliminando i ritardi dalle e alle applicazioni basate sul cloud. Allo stesso modo, un sistema di sicurezza basato sull'edge o una serratura intelligente della porta di casa può continuare a funzionare anche quando la connessione al cloud si interrompe, accidentalmente o intenzionalmente. In molti casi, l'uso dell'edge computing in una qualsiasi di queste applicazioni può contribuire a ridurre i costi operativi complessivi mitigando la dipendenza del prodotto dalle risorse del cloud. Invece di dover far fronte a un'inaspettata necessità di ulteriori e costose risorse cloud all'aumento della domanda di prodotti, gli sviluppatori possono fare affidamento sulle capacità di elaborazione locale integrate nei prodotti per contenere le spese operative.

La rapida accettazione e l'aumento della domanda di modelli di inferenza di apprendimento automatico (ML) amplifica notevolmente l'importanza dell'edge computing. Per gli sviluppatori, l'elaborazione locale dei modelli di inferenza aiuta a ridurre la latenza della risposta e i costi delle risorse cloud necessarie per l'inferenza basata sul cloud. Per gli utenti, l'uso di modelli di inferenza locale infonde fiducia nei prodotti, che continueranno a funzionare nonostante la perdita occasionale di connettività Internet o i cambiamenti nell'offerta cloud del fornitore. Inoltre, le preoccupazioni relative alla sicurezza e alla privacy possono ulteriormente spingere la necessità di elaborazione locale e inferenza per limitare la quantità di informazioni sensibili trasferite al cloud attraverso la rete Internet pubblica.

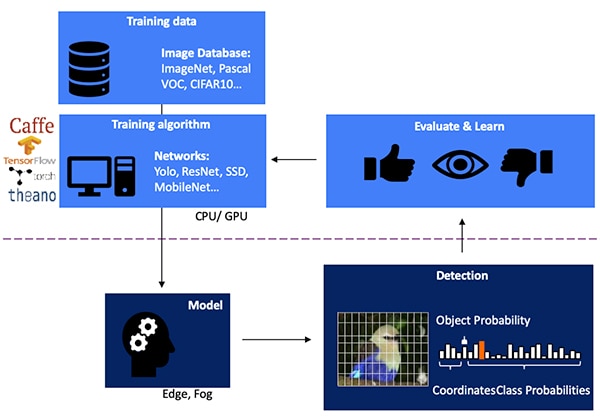

Lo sviluppo di un modello di inferenza NN per il rilevamento di oggetti basato sulla visione è un processo a più fasi che inizia con l'addestramento del modello, tipicamente eseguito su un framework ML come TensorFlow utilizzando immagini etichettate pubblicamente disponibili o personalizzate. A causa delle esigenze di elaborazione, l'addestramento dei modelli viene eseguita tipicamente con unità di elaborazione grafica (GPU) nel cloud o in un'altra piattaforma di elaborazione ad alte prestazioni. Al termine dell'addestramento, il modello viene convertito in un modello di inferenza in grado di funzionare su risorse di edge computing o fog computing e di fornire i risultati dell'inferenza come un insieme di probabilità della classe oggetto (Figura 1).

Figura 1: L'implementazione di un modello di inferenza per l'Edge IA avviene alla fine di un processo a più fasi che richiede l'addestramento e l'ottimizzazione di NN su framework che utilizzano corpus di dati disponibili o personalizzati. (Immagine per gentile concessione di Microchip Technology)

Figura 1: L'implementazione di un modello di inferenza per l'Edge IA avviene alla fine di un processo a più fasi che richiede l'addestramento e l'ottimizzazione di NN su framework che utilizzano corpus di dati disponibili o personalizzati. (Immagine per gentile concessione di Microchip Technology)

Perché i modelli di inferenza sono complessi dal punto di vista computazionale

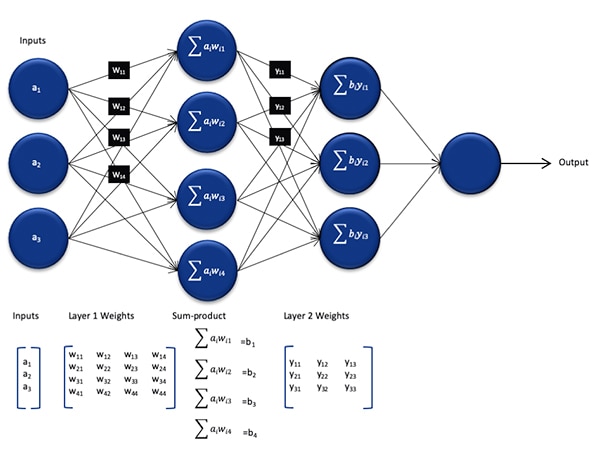

Sebbene ridotto nelle dimensioni e nella complessità rispetto al modello utilizzato durante il processo di addestramento, un modello di inferenza NN è comunque una sfida computazionale per i processori generici, a causa del gran numero di calcoli che richiede. Nella sua forma generica, un modello NN profondo comprende più strati di insiemi di neuroni. All'interno di ogni strato in una rete completamente connessa, ogni neurone nij deve calcolare la somma dei prodotti di ogni input con un peso wij associato (Figura 2).

Figura 2: Il numero di calcoli necessari per l'inferenza con una NN può imporre un carico di lavoro computazionale significativo. (Immagine per gentile concessione di Microchip Technology)

Figura 2: Il numero di calcoli necessari per l'inferenza con una NN può imporre un carico di lavoro computazionale significativo. (Immagine per gentile concessione di Microchip Technology)

Non mostrato in Figura 2 è il requisito computazionale aggiuntivo imposto dalla funzione di attivazione che modifica l'output di ogni neurone mappando i valori negativi a zero, i valori maggiori di 1 a 1 e funzioni simili. L'output della funzione di attivazione per ogni nij neuronale serve da input per il livello successivo i+1, continuando in questo modo per ogni livello. Infine, lo strato di output del modello NN produce un vettore di output che rappresenta la probabilità che il vettore di input originale (o matrice) corrisponda a una delle classi (o etichette) utilizzate durante il processo di apprendimento supervisionato.

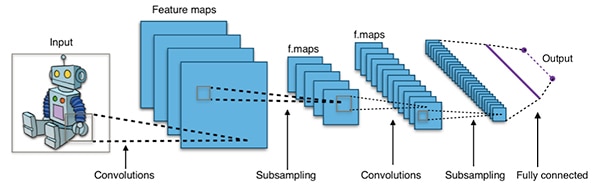

I modelli NN efficaci sono costruiti con architetture molto più grandi e complesse rispetto all'architettura generica rappresentativa NN mostrata sopra. Ad esempio, una tipica NN convoluzionale (CNN) utilizzata per il rilevamento di oggetti immagine applica questi principi in modo frammentario, scansionando la larghezza, l'altezza e la profondità del colore di un'immagine in ingresso per produrre una serie di mappe di caratteristiche che generino infine il vettore predittivo risultante (Figura 3).

Figura 3: Le CNN utilizzate per il rilevamento di oggetti immagine coinvolgono un gran numero di neuroni in molti strati, imponendo così una maggiore domanda alla piattaforma di calcolo. (Immagine per gentile concessione di Aphex34 CC BY-SA 4.0)

Figura 3: Le CNN utilizzate per il rilevamento di oggetti immagine coinvolgono un gran numero di neuroni in molti strati, imponendo così una maggiore domanda alla piattaforma di calcolo. (Immagine per gentile concessione di Aphex34 CC BY-SA 4.0)

Utilizzo degli FPGA per accelerare la matematica di NN

Sebbene continuino ad emergere numerose opzioni per l'esecuzione di modelli di inferenza sull'edge, poche alternative offrono il mix ottimale di flessibilità, prestazioni ed efficienza energetica necessario per l'inferenza ad alta velocità sull'edge. Tra le alternative prontamente disponibili per l'Edge IA, gli FPGA sono particolarmente efficaci perché possono fornire l'esecuzione ad alte prestazioni - basata su hardware - di operazioni ad alta intensità di calcolo, e consumano relativamente poca energia.

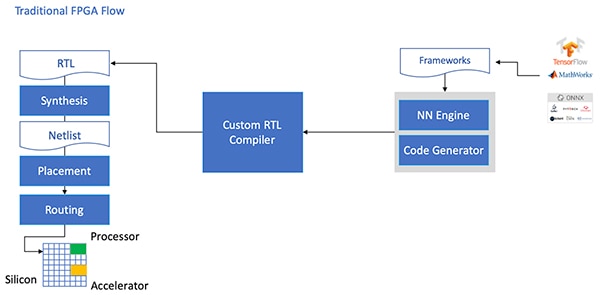

Nonostante i loro vantaggi, gli FPGA sono talvolta trascurati a causa di un flusso di sviluppo tradizionale che può essere scoraggiante per gli sviluppatori senza una vasta esperienza in fatto di FPGA. Per un'efficace implementazione FPGA di un modello NN generato da un framework NN, lo sviluppatore deve conoscere le sfumature implicite nella conversione del modello nel linguaggio di trasferimento dei registri (RTL), sintetizzando il progetto e lavorando fino alla fase finale di progettazione fisica del punto e del percorso per produrre un'implementazione ottimizzata (Figura 4).

Figura 4: Per implementare un modello NN su un FPGA, gli sviluppatori finora dovevano capire come convertire i loro modelli in RTL e lavorare attraverso il tradizionale flusso FPGA. (Immagine per gentile concessione di Microchip Technology)

Figura 4: Per implementare un modello NN su un FPGA, gli sviluppatori finora dovevano capire come convertire i loro modelli in RTL e lavorare attraverso il tradizionale flusso FPGA. (Immagine per gentile concessione di Microchip Technology)

Con i suoi FPGA PolarFire, software specializzato e la proprietà intellettuale (IP) associata, Microchip Technology fornisce una soluzione che rende l'inferenza ad alte prestazioni e bassa potenza sull'edge ampiamente disponibile per gli sviluppatori senza esperienza con gli FPGA.

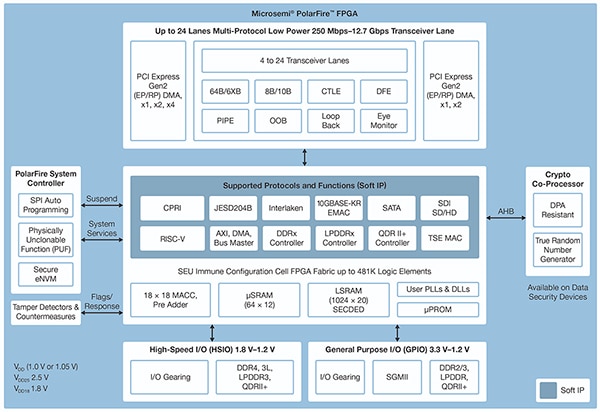

Realizzati con un'avanzata tecnologia di processo non volatile, gli FPGA PolarFire sono progettati per massimizzare la flessibilità e le prestazioni, riducendo al minimo il consumo energetico. Insieme a una vasta gamma di interfacce ad alta velocità per le comunicazioni e l'ingresso/uscita (I/O), sono dotati di un tessuto FPGA profondo in grado di supportare funzionalità avanzate utilizzando soft core IP, inclusi processori RISC-V, controller di memoria avanzati e altri sottosistemi di interfaccia standard (Figura 5).

Figura 5: L'architettura PolarFire di Microchip Technology fornisce un tessuto profondo progettato per supportare i requisiti di progettazione ad alte prestazioni, compresa l'implementazione di modelli di inferenza ad alta intensità di calcolo. (Immagine per gentile concessione di Microchip Technology)

Figura 5: L'architettura PolarFire di Microchip Technology fornisce un tessuto profondo progettato per supportare i requisiti di progettazione ad alte prestazioni, compresa l'implementazione di modelli di inferenza ad alta intensità di calcolo. (Immagine per gentile concessione di Microchip Technology)

Il tessuto FPGA PolarFire fornisce un'ampia serie di elementi logici e blocchi specializzati, supportati in una gamma di capacità da diversi membri della famiglia di FPGA PolarFire, incluse le serie MPF100T, MPF200T, MPF300T e MPF500T (Tabella 1).

|

Tabella 1: Nella serie PolarFire sono disponibili diverse caratteristiche e capacità del tessuto FPGA. (Tabella per gentile concessione di DigiKey, basata sulla scheda tecnica PolarFire di Microchip Technology)

Tra le caratteristiche di particolare interesse per l'accelerazione di inferenza, l'architettura PolarFire include un blocco matematico dedicato che fornisce una funzione di accumulazione multipla (MAC) firmata a 18 bit × 18 bit con un pre-addizionatore. Una modalità incorporata di prodotto scalare utilizza un singolo blocco matematico per eseguire due operazioni di moltiplicazione a 8 bit, fornendo un meccanismo per aumentare la capacità sfruttando l'impatto trascurabile della quantizzazione del modello sulla precisione.

Oltre ad accelerare le operazioni matematiche, l'architettura PolarFire aiuta ad alleviare la congestione di memoria quando si implementano modelli di inferenza su architetture di uso generale, come piccole memorie distribuite per la memorizzazione dei risultati intermedi creati durante l'esecuzione dell'algoritmo NN. Inoltre, i pesi e i valori di polarizzazione di un modello NN possono essere memorizzati in una memoria di sola lettura (ROM) a profondità 16 per un coefficiente di 18 bit creata a partire da elementi logici situati vicino al blocco matematico.

In combinazione con altre caratteristiche del tessuto FPGA PolarFire, i blocchi matematici forniscono la base per l'IP CoreVectorBlox di alto livello di Microchip Technology. Questo serve da motore NN flessibile in grado di eseguire diversi tipi di NN. Insieme a una serie di registri di controllo, l'IP CoreVectorBlox comprende tre blocchi funzionali principali:

- Microcontroller: un semplice processore soft RISC-V che legge il grande oggetto binario (BLOB) del firmware Microchip e il file NN BLOB specifico dell'utente dalla memoria esterna. Controlla le operazioni complessive di CoreVectorBlox eseguendo le istruzioni dal BLOB firmware.

- Processore a matrice (MXP): un processore soft che comprende otto unità logiche aritmetiche (ALU) a 32 bit e progettato per eseguire operazioni parallele su vettori di dati utilizzando operazioni con tensori element-wise, tra cui add, sub, xor, shift, mul, dotprod e altre, utilizzando una precisione mista a 8 bit, 16 bit e 32 bit, a seconda dei casi.

- Acceleratore CNN: accelera le operazioni MXP mediante un array bidimensionale di funzioni MAC implementate usando blocchi matematici con una precisione a 8 bit.

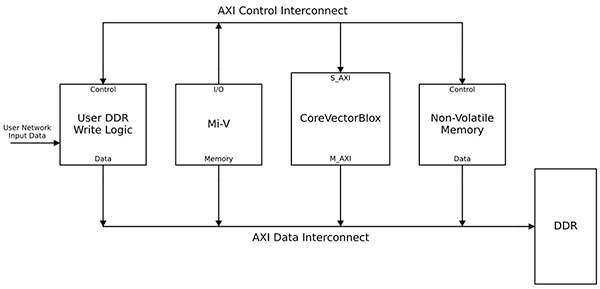

Un sistema completo di elaborazione NN in teoria dovrebbe combinare un blocco IP CoreVectorBlox, memoria, controller di memoria e un processore host, come il core di processore software Microsoft RISC-V (Mi-V) (Figura 6).

Figura 6: Il blocco IP CoreVectorBlox funziona con un processore host come il microcontroller Mi-V RISC-V di Microchip per implementare un modello di inferenza NN. (Immagine per gentile concessione di Microchip Technology)

Figura 6: Il blocco IP CoreVectorBlox funziona con un processore host come il microcontroller Mi-V RISC-V di Microchip per implementare un modello di inferenza NN. (Immagine per gentile concessione di Microchip Technology)

In un'implementazione di sistema video, il processore host carica il firmware e i BLOB di rete dalla memoria flash del sistema e li copia nella memoria ad accesso casuale (RAM) a doppia velocità dati (DDR) per l'uso da parte del blocco CoreVectorBlox. All'arrivo dei fotogrammi video, il processore host li scrive nella RAM DDR e segnala al blocco CoreVectorBlox di iniziare l'elaborazione dell'immagine. Dopo aver eseguito il modello di inferenza definito nel BLOB di rete, il blocco CoreVectorBlox scrive i risultati, inclusa la classificazione delle immagini, nella RAM DDR per l'uso da parte dell'applicazione di destinazione.

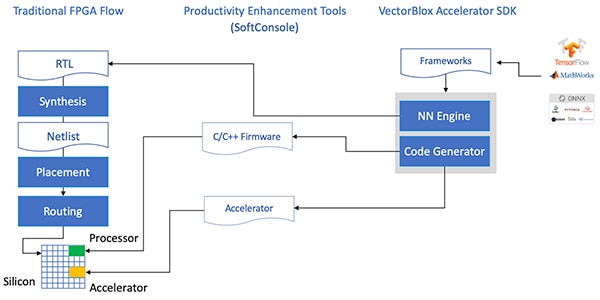

Il flusso di sviluppo semplifica l'implementazione di FPGA NN

Microchip risparmia agli sviluppatori la complessità di implementare un modello di inferenza NN sugli FPGA PolarFire. Invece di occuparsi dei dettagli del tradizionale flusso FPGA, gli sviluppatori di un modello NN lavorano con i loro framework NN come al solito e caricano il modello risultante nel kit di sviluppo software VectorBlox Accelerator di Microchip Technology. Questo SDK genera tutti i file necessari, compresi quelli necessari per il normale flusso di sviluppo FPGA e i file BLOB del firmware e della rete di cui sopra (Figura 7).

Figura 7: L'SDK VectorBlox Accelerator gestisce i dettagli dell'implementazione di un modello NN su un FPGA, generando automaticamente i file necessari per progettare ed eseguire il modello di inferenza basato su FPGA. (Immagine per gentile concessione di Microchip Technology)

Figura 7: L'SDK VectorBlox Accelerator gestisce i dettagli dell'implementazione di un modello NN su un FPGA, generando automaticamente i file necessari per progettare ed eseguire il modello di inferenza basato su FPGA. (Immagine per gentile concessione di Microchip Technology)

Poiché il flusso dell'SDK VectorBlox Accelerator si sovrappone al progetto NN sul motore NN implementato nell'FPGA, diversi NN possono funzionare sullo stesso progetto FPGA senza la necessità di ripetere il flusso di sintesi del progetto FPGA. Gli sviluppatori creano il codice C/C++ per il sistema risultante e possono cambiare al volo i modelli all'interno del sistema o eseguirli in simultanea usando la tecnica di time slicing.

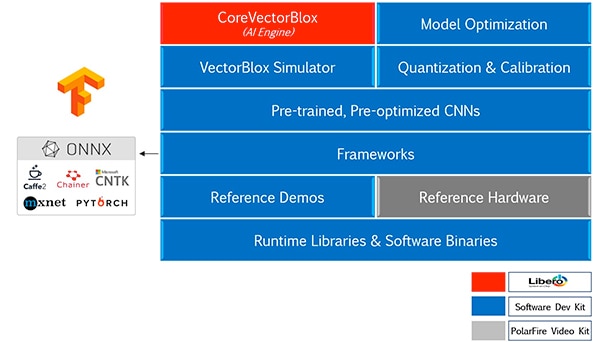

L'SDK VectorBlox Accelerator unisce la suite di progettazione FPGA Libero di Microchip Technology a una serie completa di funzionalità per lo sviluppo di modelli di inferenza NN. Insieme all'ottimizzazione del modello, alla quantizzazione e ai servizi di calibrazione, l'SDK fornisce un simulatore NN che permette agli sviluppatori di utilizzare gli stessi file BLOB per valutare il loro modello prima dell'utilizzo nell'implementazione hardware dell'FPGA (Figura 8).

Figura 8: L'SDK VectorBlox Accelerator fornisce una serie completa di servizi progettati per ottimizzare l'implementazione in FPGA di modelli di inferenza generati dal framework. (Immagine per gentile concessione di Microchip Technology)

Figura 8: L'SDK VectorBlox Accelerator fornisce una serie completa di servizi progettati per ottimizzare l'implementazione in FPGA di modelli di inferenza generati dal framework. (Immagine per gentile concessione di Microchip Technology)

L'SDK VectorBlox Accelerator supporta modelli nel formato Open Neural Network Exchange (ONNX) e modelli provenienti da una serie di framework tra cui TensorFlow, Caffe, Chainer, PyTorch e MXNET. Le architetture CNN supportate includono MNIST, versioni MobileNet, ResNet-50, Tiny Yolo V2 e Tiny Yolo V3. Microchip si sta adoperando all'ampliamento del supporto con l'inclusione della maggior parte delle reti nel toolkit OpenVINO open-source che fa parte del panorama di modelli aperti e pre-formati comprendente tra gli altri Yolo V3, Yolo V4, RetinaNet e SSD-MobileNet.

Il kit video dimostra l'inferenza FPGA

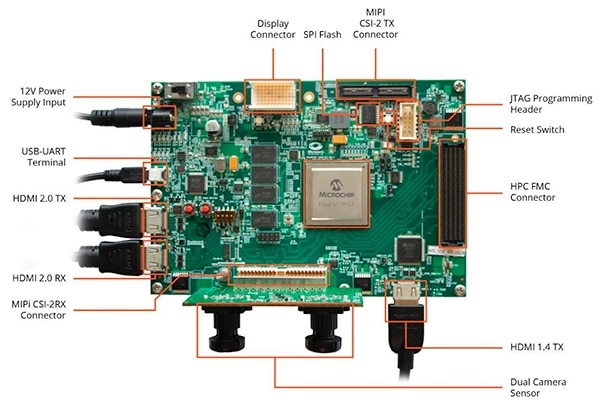

Per aiutare gli sviluppatori a passare rapidamente allo sviluppo di applicazioni di visione embedded intelligenti, Microchip Technology fornisce un'applicazione di esempio completa e progettata per l'esecuzione su MPF300-VIDEO-KIT, il kit video/immagini e progetto di riferimento per FPGA PolarFire.

Basata sull'FPGA MPF300T PolarFire di Microchip, la scheda del kit combina un doppio sensore fotocamera, RAM doppia velocità dati 4 (DDR4), memoria flash, gestione dell'alimentazione e una varietà di interfacce (Figura 9).

Figura 9: Il kit video/immagini per FPGA PolarFire MPF300-VIDEO-KIT di Microchip e il software associato forniscono agli sviluppatori un modo veloce per iniziare l'inferenza basata su FPGA nelle applicazioni di visione embedded intelligenti. (Immagine per gentile concessione di Microchip Technology)

Figura 9: Il kit video/immagini per FPGA PolarFire MPF300-VIDEO-KIT di Microchip e il software associato forniscono agli sviluppatori un modo veloce per iniziare l'inferenza basata su FPGA nelle applicazioni di visione embedded intelligenti. (Immagine per gentile concessione di Microchip Technology)

Il kit viene fornito con un progetto Libero completo utilizzato per generare il firmware e i file BLOB di rete. Dopo aver programmato i file BLOB nella memoria flash sulla scheda, basta cliccare il pulsante di esecuzione in Libero per avviare la dimostrazione, che elabora le immagini video dal sensore fotocamera e visualizza i risultati dell'inferenza su un display (Figura 10).

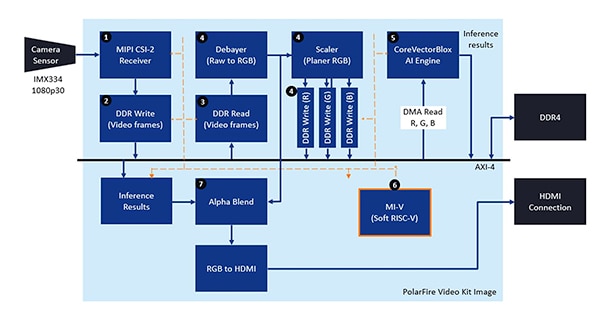

Figura 10: Il kit video/immagini per FPGA PolarFire di Microchip Technology dimostra come progettare e utilizzare un'implementazione FPGA di un sistema di visione embedded intelligente incentrato sul motore NN CoreVectorBlox di Microchip. (Immagine per gentile concessione di Microchip Technology)

Figura 10: Il kit video/immagini per FPGA PolarFire di Microchip Technology dimostra come progettare e utilizzare un'implementazione FPGA di un sistema di visione embedded intelligente incentrato sul motore NN CoreVectorBlox di Microchip. (Immagine per gentile concessione di Microchip Technology)

Per ogni fotogramma video in ingresso, il sistema basato su FPGA esegue i passi seguenti (i numeri sono correlati alla Figura 10):

- Carica un fotogramma dalla telecamera

- Memorizza il fotogramma nella RAM

- Legge il fotogramma dalla RAM

- Converte l'immagine grezza in RGB e memorizza il risultato nella RAM

- Il processore soft Mi-V soft RISC-V avvia il motore CoreVectorBlox, che recupera l'immagine dalla RAM, esegue l'inferenza e memorizza i risultati della probabilità di classificazione nella RAM

- Il Mi-V utilizza i risultati per creare un fotogramma in overlay con riquadri di delimitazione, risultati della classificazione e altri metadati e memorizza il fotogramma nella RAM

- Il fotogramma originale viene unito a quello in overlay e scritto sul display HDMI

La dimostrazione supporta l'accelerazione dei modelli Tiny Yolo V3 e MobileNet V2, ma gli sviluppatori possono eseguire altri modelli supportati dall'SDK utilizzando i metodi descritti in precedenza, apportando una piccola modifica al codice per aggiungere il nome del modello e i metadati all'elenco esistente con i due modelli predefiniti.

Conclusione

Gli algoritmi di IA, come i modelli NN, impongono tipicamente carichi di lavoro ad alta intensità di calcolo che richiedono risorse di calcolo più robuste rispetto a quelle disponibili con i processori generici. Mentre gli FPGA sono ben equipaggiati per soddisfare i requisiti di prestazioni e bassa potenza richiesti dall'esecuzione dei modelli di inferenza, i metodi di sviluppo FPGA convenzionali possono sembrare complessi e spesso inducono gli sviluppatori a rivolgersi a soluzioni men che ottimali.

Come mostrato, utilizzando IP e software specializzati di Microchip Technology, gli sviluppatori senza esperienza in fatto di FPGA possono implementare progetti basati sull'inferenza in grado di soddisfare meglio i requisiti di prestazione, potenza e tempi di progettazione.

Esonero della responsabilità: le opinioni, le convinzioni e i punti di vista espressi dai vari autori e/o dai partecipanti al forum su questo sito Web non riflettono necessariamente le opinioni, le convinzioni e i punti di vista di DigiKey o le sue politiche.