Implementazione di generatori di clock programmabili ad alte prestazioni per data center e sistemi industriali

La temporizzazione precisa è fondamentale per supportare le comunicazioni Ethernet e Peripheral Component Interconnect Express (PCIe) e può richiedere un certo impegno quando si progettano server, sistemi di archiviazione e sistemi industriali embedded o per la connettività di rete. Non basta aggiungere un bus Ethernet o PCIe. Un progetto tipico può avere diversi bus, tutti con la necessità di un supporto di temporizzazione preciso con un jitter minimo. Un sistema tipico richiede un mix di bus di comunicazione che operano a varie frequenze fino a 650 MHz.

Servono soluzioni che occupino il minor spazio possibile sulle schede a circuiti stampati. Inoltre, le esigenze di temporizzazione di Ethernet e PCIe sono diverse, il che rende la sfida della progettazione un po' più ardua. Per rispondere a queste esigenze, ci si può rivolgere a CI compatti e programmabili per la generazione di clock, che possono fornire simultaneamente fino a 12 clock di riferimento per i bus Ethernet e PCIe.

Questo blog esamina brevemente alcune delle esigenze relative alla temporizzazione dei bus Ethernet e PCIe, quindi presenta una serie di soluzioni compatte programmabili per la generazione di clock di Renesas, idonee per supportare simultaneamente le esigenze di più bus PCIe ed Ethernet. Presenteremo anche schede di valutazione per accelerare lo sviluppo di circuiti di temporizzazione nei server, nei sistemi di archiviazione e nei sistemi industriali di rete o embedded.

Controllo del jitter e massimo contenimento delle EMI

PCIe ed Ethernet sono tecnologie utilizzate per scopi diversi. Le applicazioni PCIe comprendono le comunicazioni da chip a chip sulle schede a circuiti stampati e le connessioni alle schede di espansione, mentre Ethernet è utilizzato per reti LAN (locali), reti SAN (storage) e applicazioni simili. I vari ambienti operativi pongono requisiti diversi ai circuiti di temporizzazione.

L'attenuazione del jitter è di fondamentale importanza nelle reti Ethernet. Ad esempio, in Ethernet ad alta velocità fino a 650 MHz, il jitter di fase quadratico medio (RMS) deve essere limitato a un massimo di 150 fs per garantire l'integrità del segnale, ritardi di propagazione ridotti e un comportamento prevedibile.

Oltre a controllare il jitter, i bus PCIe traggono vantaggio dall'uso della modulazione a divisione di spettro che distribuisce l'energia del jitter su un campo di frequenze più ampio, riducendo al minimo le interferenze elettromagnetiche (EMI). Controllare le EMI significa ridurre la necessità di schermare le schede, con conseguente contenimento dei costi di sistema e accelerazione dell'integrazione. I generatori VersaClock di Renesas consentono di controllare la quantità di modulazione a divisione di spettro per ottimizzare i compromessi costi-prestazioni richiesti da applicazioni specifiche.

Fare di più in meno spazio

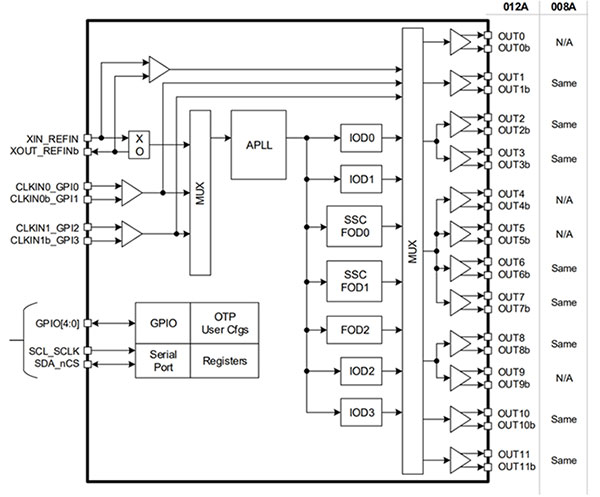

Una soluzione di temporizzazione integrata basata sui generatori VersaClock di Renesas consente di fare di più pur occupando meno spazio sulla scheda. Sono disponibili con 8 o 12 clock indipendenti e presentano le seguenti caratteristiche (Figura 1):

- Jitter di fase di 169 fs RMS (10 kHz - 20 MHz, 156,25 MHz)

- Clock comune PCIe Gen6 (CC) 27 fs RMS

- Supporto per il funzionamento SRIS (clock di riferimento separato a divisione indipendente (SRIS) e SRnS (clock di riferimento separato senza divisione (SRnS) PCIe

- Uscite di segnalazione differenziale a bassa tensione (LVDS) da 1 kHz a 650 MHz e logica di direzionamento della corrente a basso consumo e alta velocità (LP-HCSL).

Figura 1: Sono disponibili generatori di clock programmabili VersaClock che supportano fino a otto clock (colonna "008A" a destra) o fino a 12 clock (colonna "012A"). (Immagine per gentile concessione di Renesas)

Figura 1: Sono disponibili generatori di clock programmabili VersaClock che supportano fino a otto clock (colonna "008A" a destra) o fino a 12 clock (colonna "012A"). (Immagine per gentile concessione di Renesas)

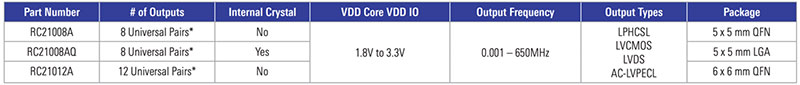

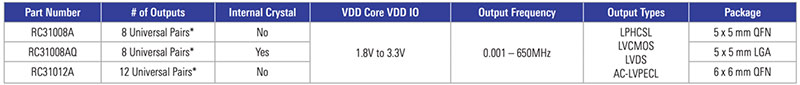

Un approccio tradizionale alla costruzione di una soluzione di temporizzazione con 5 clock indipendenti richiede un circuito oscillatore a cristallo comune che occupa circa 3x3 mm di spazio sulla scheda più quattro sub-oscillatori, ciascuno dei quali occupa circa 5x3 mm. In alternativa è possibile utilizzare un singolo CI VersaClock come RC21008A che occupa solo 5x5 mm. E questo stesso CI può supportare fino a otto uscite di clock, riducendo ulteriormente lo spazio sulla scheda, il numero di componenti e il costo. La Tabella 1 mostra le caratteristiche principali di RC21008A con altri due circuiti integrati della famiglia VersaClock 7: RC21008AQ e RC21012A.

Tabella 1: Le caratteristiche chiave di 3 generatori di clock della famiglia VersaClock 7; "*" indica che le uscite sono configurabili come differenziali o LVCMOS. (Tabella per gentile concessione di Renesas)

Tabella 1: Le caratteristiche chiave di 3 generatori di clock della famiglia VersaClock 7; "*" indica che le uscite sono configurabili come differenziali o LVCMOS. (Tabella per gentile concessione di Renesas)

Attenuazione del jitter

Gli attenuatori di jitter programmabili RC31008A, RC31008AQ e RC31012A hanno funzionalità di sincronizzazione di rete, tra cui JEDEC JESD204B/C per il supporto della sincronizzazione del convertitore su uscite a terminazione singola o differenziali con accoppiamento c.a. o c.c., e il supporto di Ethernet sincrono (SyncE) per la sincronizzazione basata sulla rete. Come i CI di generazione di clock VersaClock, questi attenuatori di jitter sono disponibili con 8 o 12 uscite, riducendo le dimensioni e il costo della soluzione (Tabella 2).

Tabella 2: Attenuatori di jitter della famiglia VersaClock 7; "*" indica il numero di uscite configurabili come differenziali o LVCMOS. (Tabella per gentile concessione di Renesas)

Tabella 2: Attenuatori di jitter della famiglia VersaClock 7; "*" indica il numero di uscite configurabili come differenziali o LVCMOS. (Tabella per gentile concessione di Renesas)

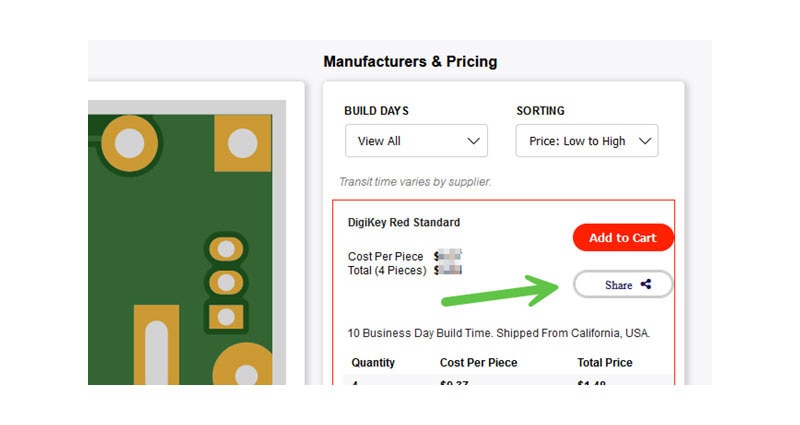

Schede di valutazione

Per accelerare il processo di sviluppo, Renesas offre una gamma di schede di valutazione (EVB), tra cui RC21008-EVB (Figura 2) e RC21012-EVB, per i progetti di generatori di clock a 8 e 12 uscite, rispettivamente, e RC31008-EVB e RC31012-EVB che possono essere utilizzate per gli attenuatori di jitter rispettivamente per 8 e 12 uscite. Queste EVB possono supportare la generazione di clock in modalità sintetizzatore per la conformità PCIe e per le caratteristiche a divisione di spettro; inoltre possono anche supportare la modalità di attenuazione del jitter. Supportano campi di frequenza dell'ingresso di riferimento da 1 kHz a 650 MHz in modo differenziale e da 1 kHz a 200 MHz in modo a terminazione singola. Presentano una dissipazione di potenza tipica inferiore a 1 W con specifiche di jitter di:

- Jitter di fase inferiore a 150 fs RMS (12 kHz-20 MHz, intero)

- Jitter di fase inferiore a 200 fs RMS (12 kHz-20 MHz, frazionario)

Figura 2: Le EVB, come RC21008-EVB per la serie 7 VersaClock, supportano lo sviluppo di otto soluzioni di uscita. (Immagine per gentile concessione di Renesas)

Figura 2: Le EVB, come RC21008-EVB per la serie 7 VersaClock, supportano lo sviluppo di otto soluzioni di uscita. (Immagine per gentile concessione di Renesas)

Conclusione

Come mostrato, i generatori di clock VersaClock e gli attenuatori di jitter di Renesas possono essere utilizzati per sviluppare soluzioni di temporizzazione ad alte prestazioni, compatte e a basso costo per i bus PCIe ed Ethernet in numerose applicazioni industriali e di elaborazione dati. Per iniziare più facilmente, sono disponibili EVB che accelerano il processo di sviluppo e riducono il time-to-market.

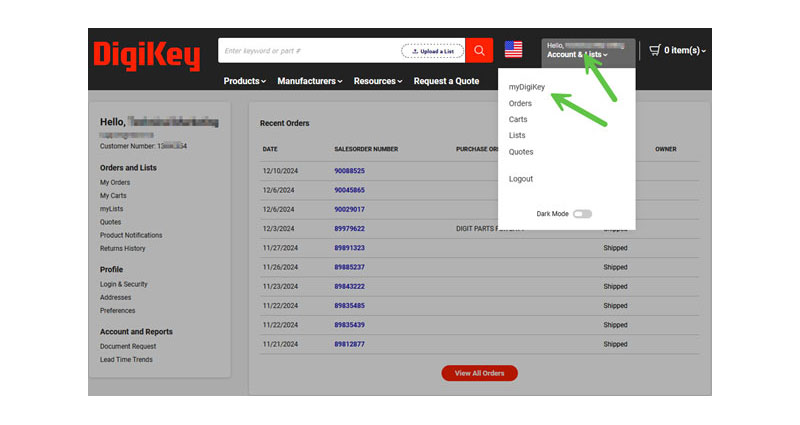

Have questions or comments? Continue the conversation on TechForum, DigiKey's online community and technical resource.

Visit TechForum